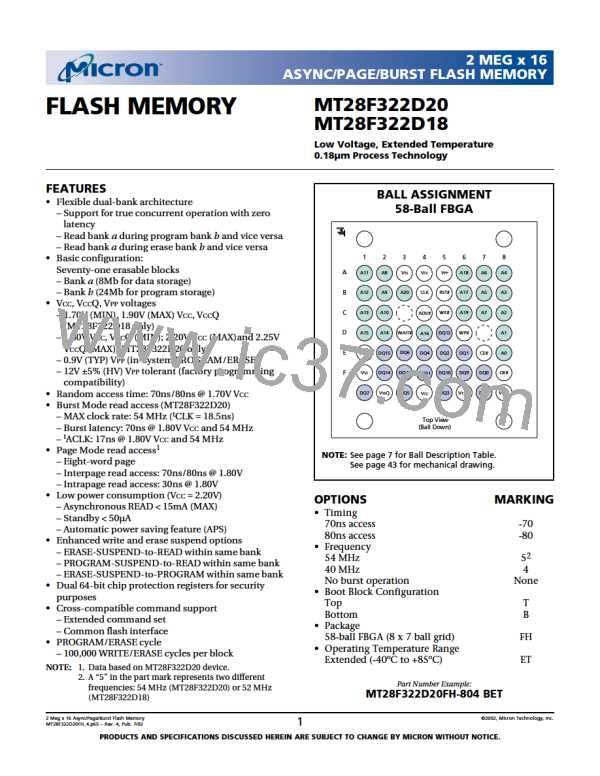

2 MEG x 16

ASYNC/PAGE/BURST FLASH MEMORY

LATENCY COUNTER

The latency counter provides the number of clocks

that must elapse after ADV# is set active before data will

be available. This value depends on the input clock fre-

quency. See Table 9 for the specific input clock frequency

configuration code. See Figure 9 also.

Table 9

Clock Frequency vs. First Access Latency

MAX

LATENCY

CLK CYCLES

SYNC

ACCESS

TIME (ns)

FREQUENCY PERIOD CONFIGURATION FOR FIRST

(MHz)

-705

(ns)

COUNTER

DATA

20

50

33

2

3

4

3

4

5

150

132

92.5

30

541

18.5

-804

20

30

40

50

33

25

2

3

4

3

4

5

150

132

125

NOTE: 1. Maximum frequency for the MT28F322D18FH-705 device is 52 MHz.

Figure 9

Latency Counter

VIH

VIL

CLK

VIH

A0–A20

VALID

ADDRESS

VIL

VIH

ADV#

DQ0–DQ15

DQ0–DQ15

DQ0–DQ15

VIL

Code 2

VOH

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

VO L

Code 3

Code 4

VOH

VO L

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

VOH

VO L

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

UNDEFINED

Figure 10

Hold Data Output Configuration

Figure 11

Wired OR WAIT# Configuration

Wired OR

CLK

WAIT#

READY#

BurstCPU/

Wait State Logic

Hold

Data

1 CLK

MT28F322D18

DQ0–DQ15

Bus data

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

VALID

OUTPUT

DQ0–DQ15

DQ0–DQ15

DATA

.

Hold

Data

2 CLK

VALID

OUTPUT

VALID

OUTPUT

.

WAIT#

MT28F322D18

DQ0–DQ15

2 Meg x 16 Async/Page/Burst Flash Memory

MT28F322D20FH_4.p65 – Rev. 4, Pub. 7/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

22

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]