MAX31865

RTD-to-Digital Converter

CS

t

CC

SCLK

t

CDD

t

t

CDD

CDH

t

DC

SDI

A7

A6

A0

t

CDZ

SDO

D7

D6

D1

D0

WRITE ADDRESS BYTE

READ DATA BYTE

NOTE: SCLK CAN BE EITHER POLARITY, TIMING SHOWN FOR CPOL = 1.

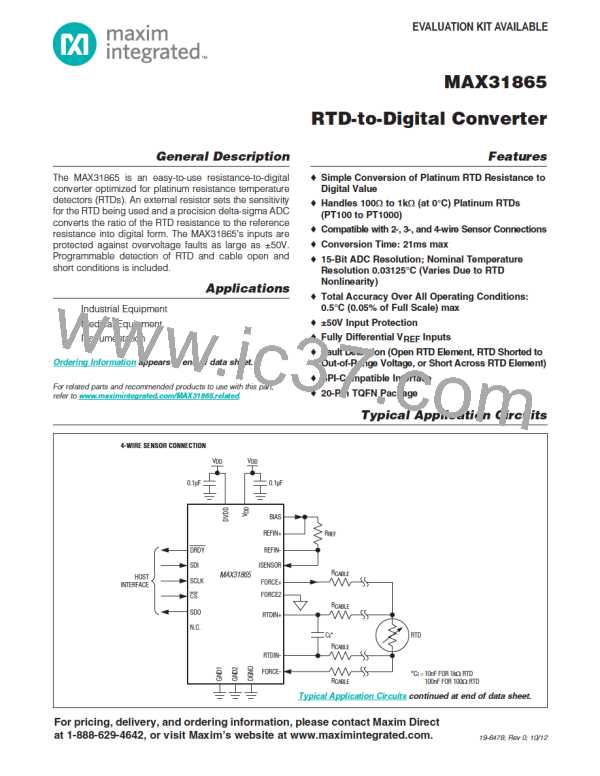

Figure 1. Timing Diagram: SPI Read Data Transfer

CS

t

CWH

t

CC

t

R

t

CCH

t

F

t

CL

SCLK

SDI

t

CDH

t

CH

t

CDH

t

DC

A7

A6

A0

D7

D0

WRITE ADDRESS BYTE

WRITE DATA BYTE

NOTE: SCLK CAN BE EITHER POLARITY, TIMING SHOWN FOR CPOL = 1.

Figure 2. Timing Diagram: SPI Write Data Transfer

Maxim Integrated

5

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]