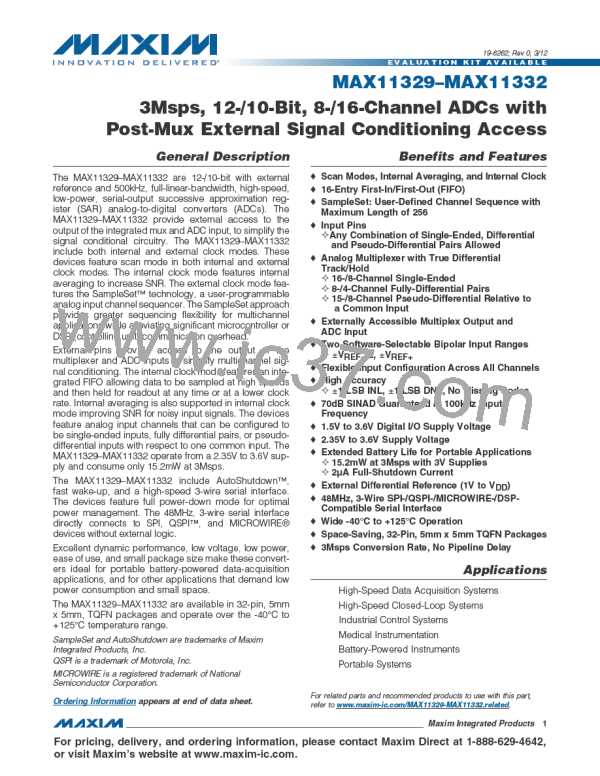

MAX11329–MAX11332

3Msps, 12-/10-Bit, 8-/16-Channel ADCs with

Post-Mux External Signal Conditioning Access

U Full shutdown where all circuitry is shutdown.

Register Descriptions

U Partial shutdown where all circuitry is powered down

The MAX11329–MAX11332 communicate between the

internal registers and the external circuitry through the

SPI-/QSPI-compatible serial interface. Table 1 details the

register access and control. Table 2 through Table 14

detail the various functions and configurations.

except for the internal bias generator.

AutoShutdown with External Clock Mode

When the PM_ bits in the ADC Mode Control register are

asserted (Table 5), the device shuts down at the rising

edge of CS in the next frame. The device powers up

again at the following falling edge of CS. There are two

available options:

For ADC mode control, set bit 15 of the register code

identification to zero. The ADC Mode Control register

determines when and under what scan condition the

ADC operates.

U AutoShutdown where all circuitry is shutdown.

U AutoStandby where all circuitry are powered down

To set the ADC data configuration, set the bit 15 of the

register code identification to one.

except for the internal bias generator.

AutoShutdown with Internal Clock Mode

The device shuts down after all conversions are complet-

ed. The device powers up again at the next falling edge

of CNVST or at the rising edge of CS after the SWCNV

bit is asserted.

Power-Down Mode

The MAX11329–MAX11332 feature three power-down

modes.

Static Shutdown

The devices shut down when the SPM bits in the ADC

Configuration register are asserted (Table 6). There are

two shutdown options:

Table 5. Power Management Modes

PM1

PM0

MODE

FUNCTION

0

0

Normal

All circuitry is fully powered up at all times.

The device enters full shutdown mode at the end of each conversion. All circuitry

is powered down. The device powers up following the falling edge of CS. It takes 2

cycles before valid conversions take place. The information in the registers is retained.

0

1

AutoShutdown

The device powers down all circuitry except for the internal bias generator. The part

powers up following the falling edge of CS. It takes 2 cycles before valid conversions

take place. The information in the registers is retained.

1

1

0

1

AutoStandby

—

Unused.

Table 6. ADC Configuration Register

DEFAULT

STATE

BIT NAME

BIT

FUNCTION

CONFIG_SETUP

15:11

N/A

Set to 10000 to select the ADC Configuration register.

REFSEL

VOLTAGE REFERENCE

REF- CONFIGURATION

REFSEL

AVGON

10

9

0

0

0

1

External single-ended

External differential

AIN15 (for the 16-channel devices)

REF-

Set to 1 to turn averaging on. Valid for internal clock mode only.

Set to 0 to turn averaging off.

���������������������������������������������������������������� Maxim Integrated Products 25

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]