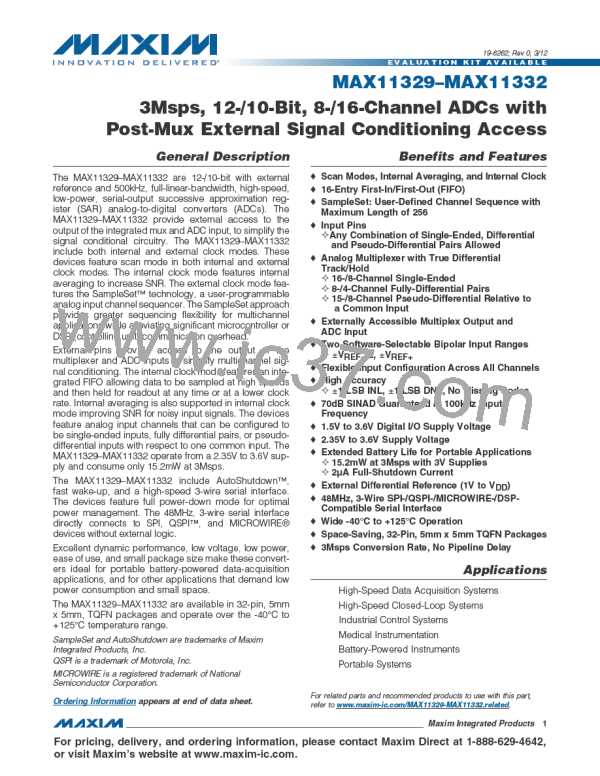

MAX11329–MAX11332

3Msps, 12-/10-Bit, 8-/16-Channel ADCs with

Post-Mux External Signal Conditioning Access

Table 7. RANGE Register (RANGE Settings Only Applies to Bipolar Fully Differential

Analog Input Configurations)

DEFAULT

STATE

BIT NAME

RANGE_SETUP

RANGE0/1

BIT

15:11

10

FUNCTION

N/A

Set to 10011 to select the RANGE register

Set to 0 for AIN0/1: +V

Set to 1 for AIN0/1: +V

/2, f = V

, f = 2(V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

0

0

0

0

0

0

0

S

Set to 0 for AIN2/3: +V

Set to 1 for AIN2/3: +V

/2, f = V

, f = 2(V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

RANGE2/3

RANGE4/5

RANGE6/7

RANGE8/9

RANGE10/11

RANGE12/13

9

8

7

6

5

4

S

Set to 0 for AIN4/5: +V

Set to 1 for AIN4/5: +V

/2, f = V

, f = 2(V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

S

Set to 0 for AIN6/7: +V

Set to 1 for AIN6/7: +V

/2, f = V

, f = 2(V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

S

Set to 0 for AIN8/9: +V

Set to 1 for AIN8/9: +V

/2, f = V

, f = 2(V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

S

Set to 0 for AIN10/11: +V

Set to 1 for AIN10/11: +V

/2, f = V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

, f = 2(V

S

Set to 0 for AIN12/13: +V

Set to 1 for AIN12/13: +V

/2, f = V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

, f = 2(V

S

Set to 0 for AIN14/15: +V

Set to 1 for AIN14/15: +V

/2, f = V

- V

- V

-

-)

REF+

REF+

S

REF+

REF+

REF

REF

RANGE14/15

—

3

0

, f = 2(V

S

2:0

000

Unused

Patterns are assembled in 4-bit channel identifier nib-

bles as described in Table 4. Figure 10 presents the

SampleSet timing diagram. Note that two CS frames are

required to configure the SampleSet functionality. The

first frame indicates the sequence length. The second

frame is used to encode the channel sequence pattern.

ADC Output as a Function

of Unipolar and Bipolar Modes

The ADC Scan Control register (Table 3) determines the

ADC mode of operation. The Unipolar and Bipolar regis-

ters in Table 10 and Table 11 determine output coding

and whether input configuration is single-ended or fully

differential.

After the SampleSet register has been coded (Table 14),

by the next falling edge of CS, the new SampleSet pattern

is activated (Figure 10). If the pattern length is less than

SEQ_LENGTH, the remaining channels default to AIN0. If

the select pattern length is greater than SEQ_LENGTH,

the additional data is ignored as the ADC waits for the ris-

ing edge of CS. If CS is asserted in the middle of a nibble,

the full nibble defaults to AIN0.

Table 9 details the conversion output for analog inputs,

AIN0 and AIN1. The truth table is consistent for any other

valid input pairs (AINn/AINn+1). Table 8 shows the appli-

cable input signal format with respect to analog input

configurations.

CHSEL[3:0] is used for MANUAL, REPEAT,

STANDARD_EXT, STANDARD_INT, UPPER_EXT,

UPPER_INT modes of operation. CHSCAN[15:0] is used

for CUSTOM_EXT and CUSTOM_INT modes of operation.

Upon receiving the SampleSet pattern, the user can

set the ADC Mode Control register to begin the conver-

sion process where data readout begins with the first

SampleSet entry. While the last conversion result is read,

the ADC can be instructed to enter AutoShutdown, if

desired. If the user wishes to change the SampleSet

length, a new pattern must be loaded into the ADC as

described in Figure 10.

SampleSet Mode of Operation

The SampleSet register stores the unique channel

sequence length. The sequence pattern is comprised of

up to 256 unique single-ended and/or differential conver-

sions with any order or pattern.

���������������������������������������������������������������� Maxim Integrated Products 27

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]