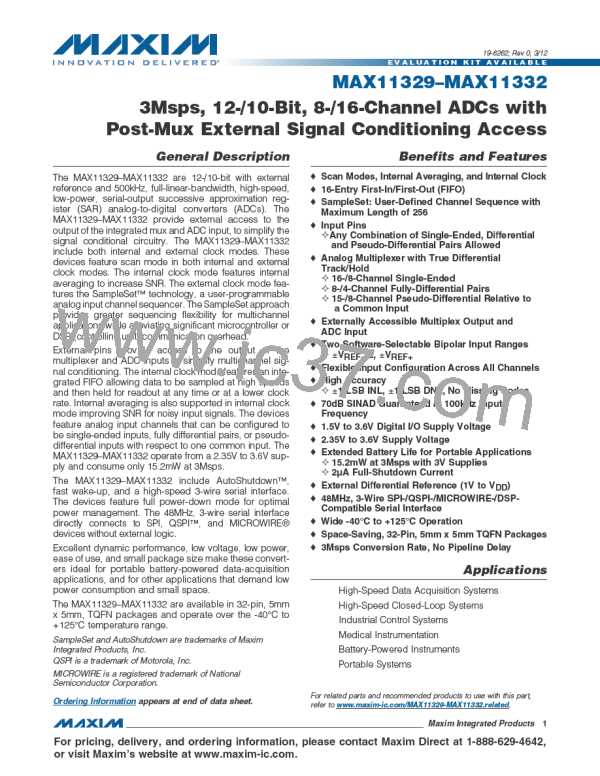

MAX11329–MAX11332

3Msps, 12-/10-Bit, 8-/16-Channel ADCs with

Post-Mux External Signal Conditioning Access

Scan Modes and Unipolar/Bipolar Setting

When the Unipolar or Bipolar registers are configured

as pseudo-differential or fully differential, the analog

input pairs are repeated in this automated mode. For

example, if N is set to 15 to scan all 16 channels and

all analog input pairs are configured for fully-differential

conversion, the ADC converts the channels twice. In this

case, the user may avoid dual conversions on input pairs

by implementing Manual mode or using Custom_Int or

Custom_Ext scan modes and only scan even (or odd)

channels (e.g. 0, 2, 4).

up to 16-channel conversions in ascending order. In this

case, the effective throughput per channel is 3Msps/16

channel or 187.5ksps. The maximum input frequency

that the ADC can resolve (Nyquist Theorem) is 93.75kHz.

If all 16 channels must be measured, with some chan-

nels having greater than 93.75kHz input frequency, the

user must revert back to manual mode requiring con-

stant communication on the serial interface. SampleSet

technology solves this problem. Figure 9 provides a

SampleSet use-model example.

Averaging Mode

In averaging mode, the device performs the specified

number of conversions and returns the average for each

requested result in the FIFO. The averaging mode works

with internal clock only.

Table 1. Register Access and Control

REGISTER IDENTIFICATION CODE

DIN ≡ DATA INPUTS

REGISTER NAME

BIT 15

BIT 14

BIT 13

BIT 12

BIT 11

BIT [10:0]

DIN

ADC Mode Control

ADC Configuration

Unipolar

0

1

1

1

1

1

1

1

1

DIN

0

DIN

0

DIN

0

DIN

0

DIN

0

0

0

1

DIN

Bipolar

0

0

1

0

DIN

RANGE

0

0

1

1

DIN

Custom Scan0

Custom Scan1

SampleSet

0

1

0

0

DIN

0

1

0

1

DIN

0

1

1

0

DIN

Reserved. Do not use.

1

1

1

1

DIN

Table 2. ADC Mode Control Register

DEFAULT

STATE

BIT NAME

BIT

FUNCTION

REG_CNTL

SCAN[3:0]

15

0

Set to 0 to select the ADC Mode Control register

ADC Scan Control register (Table 3)

14:11

0001

Analog Input Channel Select register (Table 4).

CHSEL[3:0]

10:7

6:5

0000

See Table 3 to determine which modes use CHSEL[3:0] for the channel scan

instruction.

RESET1

RESET0

FUNCTION

0

0

1

1

0

1

0

1

No reset

RESET[1:0]

00

Reset the FIFO only (resets to zero)

Reset all registers to default settings (includes FIFO)

Unused

���������������������������������������������������������������� Maxim Integrated Products 21

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]