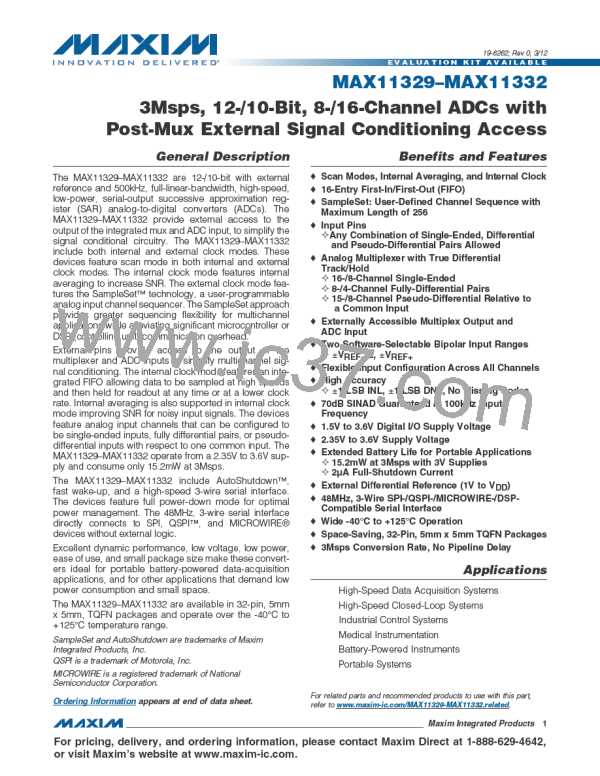

MAX11329–MAX11332

3Msps, 12-/10-Bit, 8-/16-Channel ADCs with

Post-Mux External Signal Conditioning Access

Table 3. ADC Scan Control (continued)

SCAN3 SCAN2 SCAN1 SCAN0

MODE NAME

FUNCTION

Scans channels 0 through N

Clock mode: External clock only

0

1

0

0

Standard_Ext

Channel scan/sequence: N channels in ascending order

Channel selection: See Table 4, CHSEL[3:0] determines channel N

Averaging: No

Scans channel N through the highest numbered channel. The FIFO

stores X conversion results where:

X = Channel 16–N

16-channel devices

8-channel devices

X = Channel 8–N

0

1

0

1

Upper_Int

Clock mode: Internal clock only

Channel scan/sequence: Channel N through the highest numbered

channel in ascending order

Channel selection: See Table 4, CHSEL[3:0] determines channel N

Averaging: Can be enabled

Scans channel N through the highest numbered channel

Clock mode: External clock only

Channel scan/sequence: Channel N through the highest numbered

channel in ascending order

0

0

1

1

1

1

0

1

Upper_Ext

Channel selection: See Table 4, CHSEL[3:0] determines channel N

Averaging: No

Scans preprogrammed channels in ascending order. The FIFO

stores conversion results for this unique channel sequence.

Clock mode: Internal clock only

Channel scan/sequence: Unique ascending channel sequence

Maximum depth: 16 conversions

Custom_Int

Channel selection: See Table 12, Custom Scan0 register and Table

13, Custom Scan1 register

Averaging: Can be enabled

Scans preprogrammed channels in ascending order

Clock mode: External clock only

Channel scan/sequence: Unique ascending channel sequence

Maximum depth: 16 conversions

1

0

0

0

Custom_Ext

Channel selection: See Table 12, Custom Scan0 register and Table

13, Custom Scan1 register

Averaging: No

���������������������������������������������������������������� Maxim Integrated Products 23

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]