2x4-Channel, Simultaneous-Sampling

12-Bit ADCs

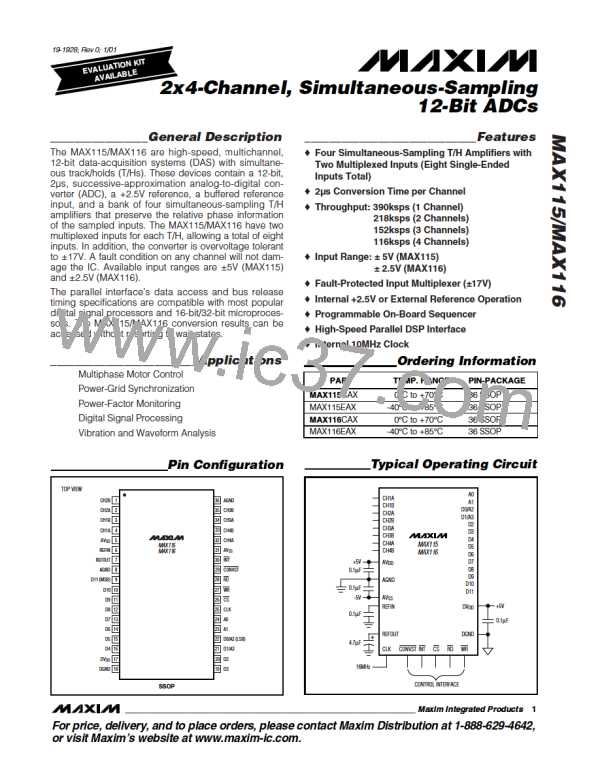

______________________________________________________________Pin Description

PIN

1, 2

3, 4

5

NAME

FUNCTION

CH2B, CH2A

CH1B, CH1A

Channel 2 Multiplexed Inputs (single-ended)

Channel 1 Multiplexed Inputs (single-ended)

AV

Analog Supply Voltage

DD

6

REFIN

REFOUT

AGND

External reference input/internal reference output. Bypass with a 0.1µF capacitor to AGND.

ꢀ

Reference-Buffer output. Bypass with a 4.ꢀµF capacitor to AGND.

8, 36

9–16

1ꢀ

Analog ground. Both pins must be connected to ground.

Data Bits. D11 = MSB.

D11–D4

DV

Digital Supply Voltage

DD

18

DGND

D3, D2

D1/A3, D0/A2

A1, A0

CLK

Digital Ground

19, 20

21, 22

23, 24

25

Data Bits

Bidirectional Data Bits/Address Bits

Address Bits

Clock Input (duty cycle must be 30ꢁ to ꢀ0ꢁ). Connect CLK to DV to activate internal clock.

DD

26

Chip-Select Input (active-low)

CS

2ꢀ

Write Input (active-low)

WR

28

Read Input (active-low)

RD

29

Conversion-Start input. Rising edge initiates sampling and conversion sequence.

Interrupt output. Falling edge indicates the end of a conversion sequence.

Analog Supply Voltage

CONVST

INT

30

31

AV

SS

32, 33

34, 35

CH4A, CH4B

CH3A, CH3B

Channel 4 Multiplexed Inputs (single-ended)

Channel 3 Multiplexed Inputs (single-ended)

_______________Detailed Description

The MAX115/MAX116 use a successive-approximation

conversion technique and four simultaneous-sampling

1.6mA

track/hold (T/H) amplifiers to convert analog signals into

12-bit digital outputs. Each T/H has two multiplexed

inputs, allowing a total of eight inputs. Each T/H output

is converted and stored in memory to be accessed

sequentially by the parallel interface with successive

read cycles. The MAX115/MAX116 internal micro-

sequencer can be programmed to digitize one, two,

three, or four inputs sampled simultaneously from either

of the two banks of four inputs (Figure 2). The

MAX115/MAX116 can operate with either an external or

internal clock. For internal operation, connect CLK to

TO OUTPUT

1.6V

PIN

120pF

1.0mA

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

DV

.

DD

6

_______________________________________________________________________________________

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]