X96010

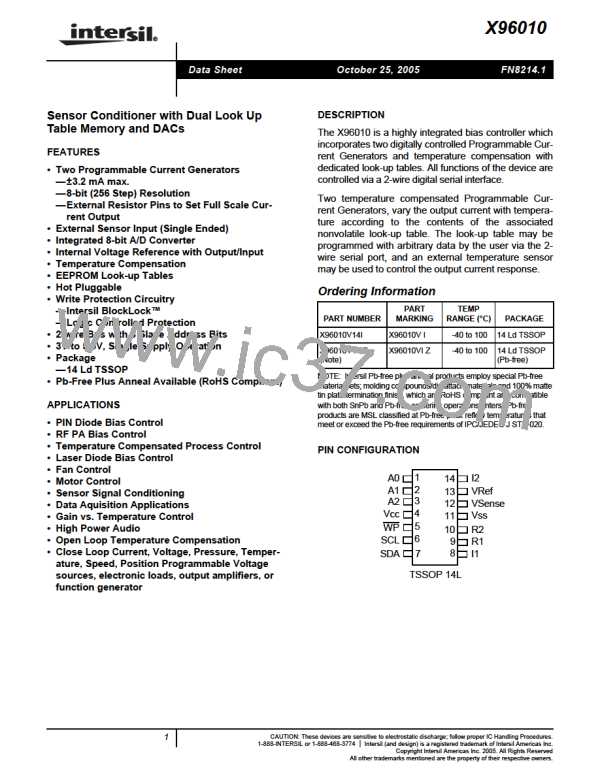

Figure 4. Control and Status Register Format

Byte

Address

MSB

7

LSB

0

Register

Name

3

6

4

2

1

5

80h

Non-Volatile

Control 0

I2DS

I1DS

NV1234 ADCfiltOff

1

VRM

0

0

I1 and I2 Direction

0: Source

1: Sink

Control

ADC

Voltage

Reference

Mode

0: Internal

1: External

filtering

0: On

1: Off

1, 2, 3, 4

Volatility

0: Volatile

1: Non-

volatile

Direct Access to LUT1

Reserved Reserved

81h

Volatile or

Non-Volatile

Control 1

Control 2

L1DA5

L2DA5

L1DA4

L2DA4

L1DA3

L2DA3

L1DA2

L2DA2

L1DA1

L2DA1

L1DA0

L2DA0

Direct Access to LUT2

Reserved Reserved

82h

Volatile or

Non-Volatile

Direct Access to DAC1

83h

Volatile or

Non-Volatile

Control 3

Control 4

Control 5

D1DA7

D1DA6

D1DA5

D2DA5

D1DA4

D2DA4

D1DA3

D2DA3

D1DA2

D2DA2

D1DA1

D2DA1

D1DA0

D2DA0

Direct Access to DAC2

84h

Volatile or

Non-Volatile

D2DA7

D2DA6

85h

Non-Volatile

D2DAS

L2DAS

D1DAS

L1DAS

0

0

0

0

Direct

Access

to DAC2

Direct

Direct

Access

to DAC1

Direct

Access

to LUT1

Access

to LUT2

0: Disabled 0: Disabled 0: Disabled 0: Disabled

1: Enabled 1: Enabled 1: Enabled 1: Enabled

86h

Volatile

Control 6

WEL

Reserved Reserved Reserved Reserved Reserved Reserved Reserved

Write

Enable

Latch

0: Write

Disabled

1: Write

Enabled

ADC Output

AD7

87h

Volatile

Status

AD6

AD5

AD4

AD3

AD2

AD1

AD0

Registers in byte addresses 88h through 8Fh are reserved.

Register bits shown as 0 or 1 should always use those values for proper operation.

FN8214.1

11

October 25, 2005

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]