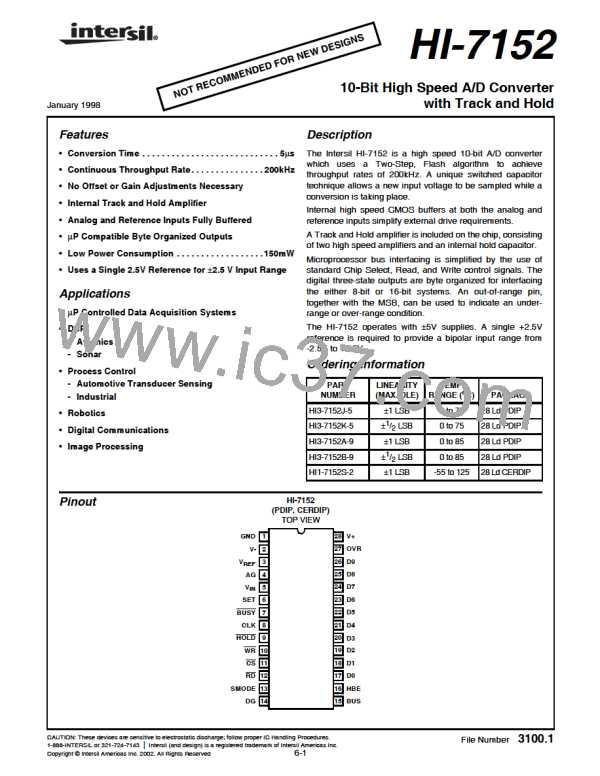

HI-7152

Timing Diagrams (Continued)

SMODE = DG, BUS = DG

0

1

2

3

4

5

6

7

CLOCK

t

CD

CS

t

SPS

t

WR

(WR MAY BE WIRED LOW)

t

t

CKHF

CKHR

HOLD

HOLD N

HOLD N+1

HOLD N+2

HOLD

TRACK N

TRACK N+1

TRACK N+2

TRACK N+3

t

DATA

INTERNAL

DATA

N DATA

N+1 DATA

RD

HBE

(HBE/LBE)

t

RD

t

AD

t

RX

D0-D9, OVR

DATA

HIGH

BYTE

LOW

BYTE

HIGH

BYTE

LOW

BYTE

N DATA

N+1 DATA

BUSY

FIGURE 1B. FAST MEMORY MODE (8-BIT DATA BUS)

SMODE = +V: RD, WR, AND CS = DG, BUS = V+, HBE = V+ OR DG

0

1

2

3

4

5

6

7

CLOCK

HOLD

TRACK N

HOLD N

TRACK N+1

N-1 DATA

HOLD N+1

TRACK N+2

N DATA

HOLD N+2

INTERNAL

DATA

N+1 DATA

BUSY

D0-D9, OVR

DATA

N-1 DATA

N DATA

N+1 DATA

FIGURE 1C. DMA MODE (16-BIT DATA BUS)

Detailed Block Diagram

5 TO 32

DECODER

(+V

)

REF

AZ

AZ

33

-

LATCH

AZ

6-8

V

+

REF

17

3

DO

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]