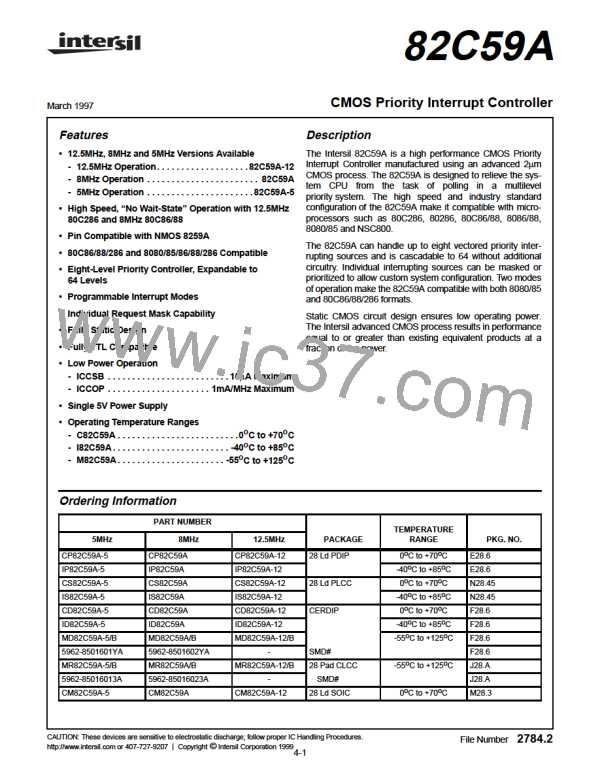

82C59A

immediately before returning from the service routine, or if After the initialization sequence, IR0 has the highest priority

the AEOI (Automatic End of Interrupt) bit is set, until the trail- and IR7 the lowest. Priorities can be changed, as will be

ing edge of the last INTA. While the IS bit is set, all further explained in the rotating priority mode or via the set priority

interrupts of the same or lower priority are inhibited, while command.

higher levels will generate an interrupt (which will be

acknowledged only if the microprocessor internal interrupt

enable flip-flop has been re-enabled through software).

OCW1

A

D

D

D

D

D

D

D

D

0

6

5

4

3

2

1

0

7

1

M

M

M

M

M

M

M

M

7

6

5

4

3

2

1

0

Interrupt Mask

1 = Mask set

0 = Mask reset

OCW2

A

0

D

D

D

D

D

D

D

0

D

6

5

4

3

2

1

7

0

R

SL

EOI

0

0

L

L

L

0

2

1

IR LEVEL TO BE

ACTED UPON

0

0

0

1

1

0

2

0

1

3

1

1

4

0

0

5

1

0

6

0

1

7

1

1

0

0

0

0

1

1

1

1

Non-specific EOI command

† Specific EOI command

0

0

1

1

0

1

0

0

1

1

1

0

End of interrupt

Rotate on non-specific EOI command

Rotate in automatic EOI mode (set)

Rotate in automatic EOI mode (clear)

Automatic rotation

Specific rotation

0

1

1

0

0

1

1

1

0

1

0

0

† Rotate on specific EOI command

† Set priority command

No operation

† L - L are used

0

2

OCW3

A

0

D

D

D

D

D

D

D

0

D

6

5

4

3

2

1

7

0

0

ESMM

SMM

0

1

P

RR

RIS

READ REGISTER COMMAND

0

0

1

0

0

1

1

1

Read IS reg on

next RD pulse

Read IR reg on

next RD pulse

No Action

1 = Poll command

0 = No poll command

SPECIAL MASK MODE

0

0

1

0

0

1

1

1

Set special

mask

Reset special

mask

No Action

FIGURE 8. 82C59A OPERATION COMMAND WORD FORMAT

4-10

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]