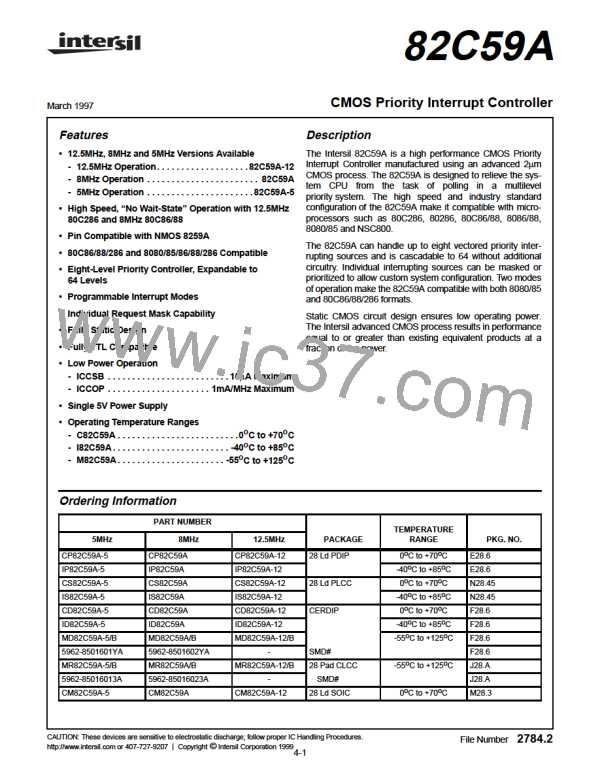

82C59A

End of Interrupt (EOI)

After Rotate (lR4 was serviced, all other priorities rotated

correspondingly)

The In-Service (IS) bit can be reset either automatically fol-

lowing the trailing edge of the last in sequence INTA pulse

(when AEOI bit in lCW1 is set) or by a command word that

must be issued to the 82C59A before returning from a ser-

vice routine (EOI Command). An EOI command must be

issued twice if servicing a slave in the Cascade mode, once

for the master and once for the corresponding slave.

IS7

IS6

1

IS5

0

IS4

0

IS3

0

IS2

0

IS1

0

IS0

0

“IS” Status

0

2

Priority

Status

1

0

7

6

5

4

3

highest

lowest

There are two forms of EOl command: Specific and Non-

Specific. When the 82C59A is operated in modes which pre-

serve the fully nested structure, it can determine which IS bit

to reset on EOI. When a Non-Specific command is issued

the 82C59A will automatically reset the highest IS bit of

those that are set, since in the fully nested mode the highest

IS level was necessarily the last level acknowledged and

serviced. A non-specific EOI can be issued with OCW2

(EOl = 1, SL = 0, R = 0).

There are two ways to accomplish Automatic Rotation using

OCW2, the Rotation on Non-Specific EOI Command (R = 1,

SL = 0, EOI = 1) and the Rotate in Automatic EOI Mode

which is set by (R = 1, SL = 0, EOI = 0) and cleared by

(R = 0, SL = 0, EOl = 0).

Specific Rotation (Specific Priority)

The programmer can change priorities by programming the

lowest priority and thus, fixing all other priorities; i.e., if IR5 is

programmed as the lowest priority device, then IR6 will have

the highest one.

When a mode is used which may disturb the fully nested

structure, the 82C59A may no longer be able to determine

the last level acknowledged. In this case a Specific End of

Interrupt must be issued which includes as part of the com-

mand the IS level to be reset. A specific EOl can be issued

with OCW2 (EOI = 1, SL = 1, R = 0, and L0 - L2 is the binary

level of the IS bit to be reset).

The Set Priority command is issued in OCW2 where: R = 1,

SL = 1, L0 - L2 is the binary priority level code of the lowest

priority device.

Observe that in this mode internal status is updated by soft-

ware control during OCW2. However, it is independent of the

End of Interrupt (EOI) command (also executed by OCW2).

Priority changes can be executed during an EOI command

by using the Rotate on Specific EOl command in OCW2

(R = 1, SL = 1, EOI = 1, and L0 - L2 = IR level to receive low-

est priority).

An lRR bit that is masked by an lMR bit will not be cleared by

a non-specific EOI if the 82C59A is in the Special Mask

Mode.

Automatic End of Interrupt (AEOI) Mode

If AEOI = 1 in lCW4, then the 82C59A will operate in AEOl

mode continuously until reprogrammed by lCW4. In this

mode the 82C59A will automatically perform a non-specific

EOI operation at the trailing edge of the last interrupt

acknowledge pulse (third pulse in 8080/85, second in

80C86/88/286). Note that from a system standpoint, this

mode should be used only when a nested multilevel interrupt

structure is not required within a single 82C59A.

Interrupt Masks

Each Interrupt Request input can be masked individually by

the Interrupt Mask Register (IMR) programmed through

OCW1. Each bit in the lMR masks one interrupt channel if it

is set (1). Bit 0 masks IR0, Bit 1 masks IR1 and so forth.

Masking an IR channel does not affect the operation of other

channels.

Automatic Rotation (Equal Priority Devices)

Special Mask Mode

In some applications there are a number of interrupting

devices of equal priority. In this mode a device, after being

serviced, receives the lowest priority, so a device requesting

an interrupt will have to wait, in the worst case until each of 7

other devices are serviced at most once. For example, if the

priority and “in service” status is:

Some applications may require an interrupt service routine

to dynamically alter the system priority structure during its

execution under software control. For example, the routine

may wish to inhibit lower priority requests for a portion of its

execution but enable some of them for another portion.

The difficulty here is that if an Interrupt Request is acknowl-

edged and an End of Interrupt command did not reset its IS

bit (i.e., while executing a service routine), the 82C59A

would have inhibited all lower priority requests with no easy

way for the routine to enable them.

Before Rotate (lR4 the highest priority requiring service)

IS7

0

IS6

1

IS5

0

IS4

1

IS3

0

IS2

0

IS1

0

IS0

0

“IS” Status

That is where the Special Mask Mode comes in. In the Spe-

cial Mask Mode, when a mask bit is set in OCW1, it inhibits

further interrupts at that level and enables interrupts from all

other levels (lower as well as higher) that are not masked.

Priority

Status

7

6

5

4

3

2

1

0

lowest

highest

Thus, any interrupts may be selectively enabled by loading

the mask register.

4-11

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]