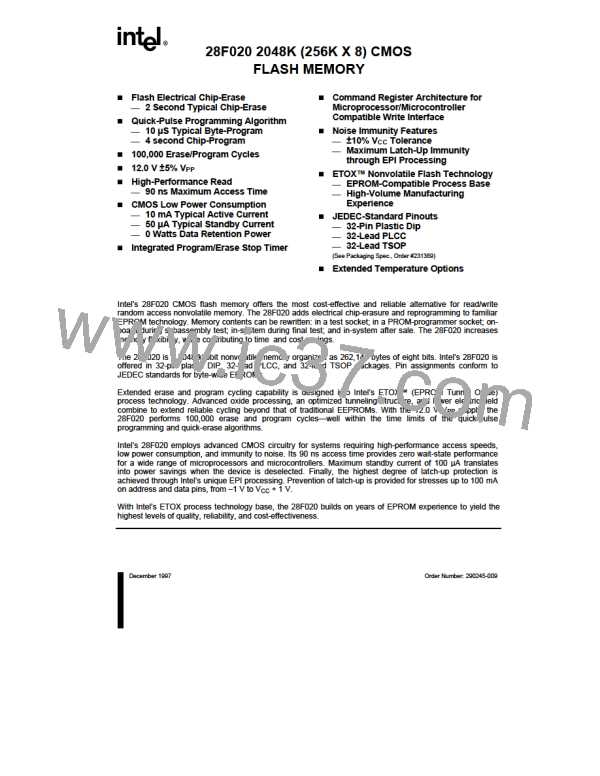

E

28F020

Start Erasure (4)

Bus

Operation

Command

Comments

Y

Entire Memory Must = 00H

Before Erasure

Data = 00H?

N

Use Quick-Pulse

Programming Algorithm

(Figure 4)

Program All

Bytes to 00H

(1)

(1)

Standby

Wait for VPP Ramp to VPPH

Apply VPPH

ADDR = 00H

PLSCNT = 0

Initialize Addresses and

Pulse-Count

Write Erase

Set-Up Cmd

Set-Up

Erase

Write

Write

Data = 20H

Data = 20H

Erase

Write Erase Cmd

Duration of Erase Operation

(tWHWH2

Stand-by

Time Out 10 ms

)

Addr = Byte to Verify;

Erase (2)

Verify

Write Erase

Verify Cmd

Write

Data = A0H; Stops Erase

(3)

Operation

Standby

Read

tWHGL

Time Out 6 µs

Read Data

Read Byte to Verify Erasure

from Device

N

Inc

N

Data = FFH?

Y

PLSCNT =

1000?

Compare Output to FFH

Increment Pulse-Count

Standby

Y

N

Increment Addr

Last Address?

Data = 00H, Resets the

Register for Read Operations

Write

Read

Y

Write Read Cmd

(1)

Standby

Wait for VPP Ramp to VPPL

(1)

(1)

Apply VPPL

Apply VPPL

Erasure

Completed

Erase Error

0245_05

NOTES:

1. See DC Characteristics for the value of VPPH and VPPL

.

2. Erase Verify is performed only after chip-erasure. A final read/compare may be performed (optional) after the register is

written with the Read command.

3. Refer of Principles of Operation.

4. Caution: The algorithm must be followed to ensure proper and reliable operation of the device.

Figure 5. 28F020 Quick-Erase Algorithm

15

INTEL [ INTEL ]

INTEL [ INTEL ]