1-Gbit P30 Family

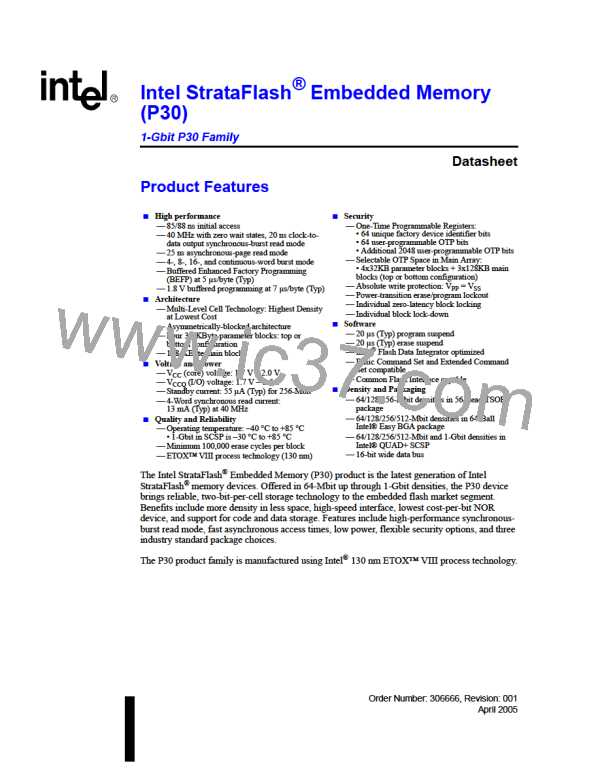

Figure 28.

CLK [C]

First-Access Latency Count

Valid

Address

Address [A]

ADV# [V]

Code 0 (Reserved)

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

DQ15-0 [D/Q]

DQ15-0 [D/Q]

DQ15-0 [D/Q]

DQ15-0 [D/Q]

DQ15-0 [D/Q]

DQ15-0 [D/Q]

DQ15-0 [D/Q]

DQ15-0 [D/Q]

Code 1

(Reserved

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Code 2

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Code 3

Code 4

Code 5

Code 6

Code 7

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Valid

Output

Table 23.

LC and Frequency Support

Latency Count Settings

Frequency Support (MHz)

2

3

≤ 27

≤ 40

See Figure 29, “Example Latency Count Setting using Code 3.

April 2005

56

Intel StrataFlash® Embedded Memory (P30)

Order Number: 306666, Revision: 001

Datasheet

INTEL [ INTEL ]

INTEL [ INTEL ]