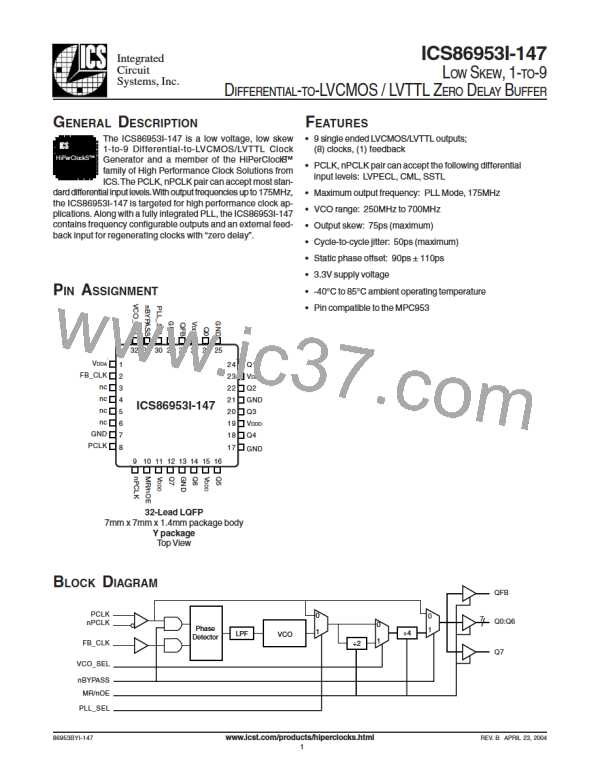

ICS86953I-147

Integrated

Circuit

Systems, Inc.

LOW

SKEW, 1-TO-9

D

IFFERENTIAL

-

TO-LVCMOS / LVTTL ZERO

DELAY

BUFFER

PCLK/nPCLK CLOCK INPUT INTERFACE

The PCLK/nPCLK accepts LVPECL, CML, SSTL and other gested here are examples only. If the driver is from another

differential signals. Both VSWING and VOH must meet the VPP vendor, use their termination recommendation. Please con-

and VCMR input requirements. Figures 3A to 3D show inter- sult with the vendor of the driver component to confirm the

face examples for the HiPerClockS PCLK/nPCLK input driven driver termination requirements.

by the most common driver types. The input interfaces sug-

2.5V

3.3V

3.3V

3.3V

2.5V

3.3V

R3

120

R4

120

R1

50

R2

50

SSTL

Zo = 60 Ohm

Zo = 60 Ohm

CML

Zo = 50 Ohm

Zo = 50 Ohm

PCLK

PCLK

nPCLK

HiPerClockS

nPCLK

PCLK/nPCLK

HiPerClockS

PCLK/nPCLK

R1

120

R2

120

FIGURE 3A. HIPERCLOCKS PCLK/NPCLK INPUT DRIVEN

BY A CML DRIVER

FIGURE 3B. HIPERCLOCKS PCLK/NPCLK INPUT DRIVEN

BY AN SSTL IN DRIVER

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

R3

125

R4

125

Zo = 50 Ohm

R3

1K

R4

1K

Zo = 50 Ohm

Zo = 50 Ohm

C1

C2

LVDS

PCLK

PCLK

R5

100

nPCLK

Zo = 50 Ohm

HiPerClockS

PCLK/nPCLK

nPCLK

HiPerClockS

Input

LVPECL

R1

1K

R2

1K

R1

84

R2

84

FIGURE 3C. HIPERCLOCKS PCLK/NPCLK INPUT DRIVEN

BY A 3.3V LVPECL DRIVER

FIGURE 3D. HIPERCLOCKS PCLK/NPCLK INPUT DRIVEN

BY A 3.3V LVDS DRIVER

86953BYI-147

www.icst.com/products/hiperclocks.html

REV. B APRIL 23, 2004

7

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]