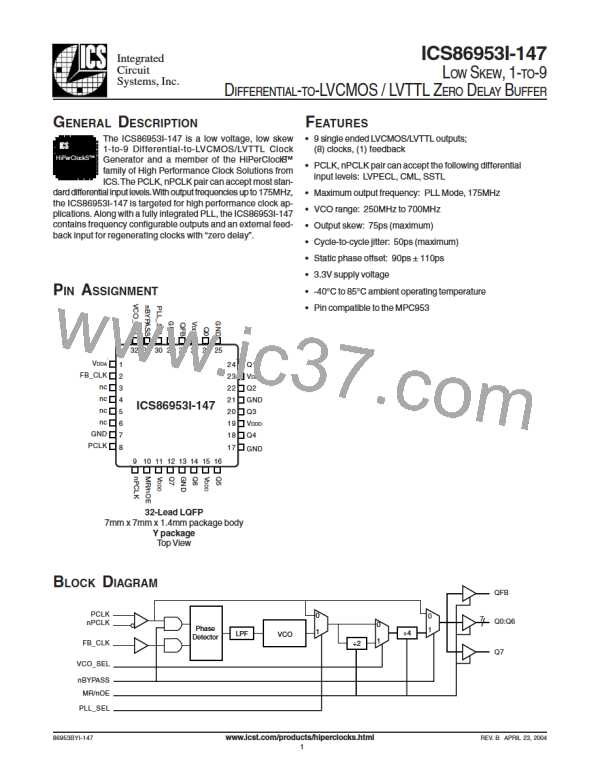

ICS86953I-147

Integrated

Circuit

Systems, Inc.

LOW

SKEW, 1-TO-9

D

IFFERENTIAL

-

TO-LVCMOS / LVTTL ZERO

DELAY

BUFFER

PARAMETER MEASUREMENT INFORMATION

1.65V 5ꢀ

VDD

SCOPE

VDDA

VDDO

,

nPCLK

Qx

VPP

VCMR

Cross Points

LVCMOS

GND

PCLK

GND

-1.65V 5ꢀ

3.3V OUTPUT LOAD AC TEST CIRCUIT

DIFFERENTIAL INPUT LEVEL

VDDO

2

VDDO

VDDO

2

VDDO

2

Q0:Q7,

QFB

Qx

2

➤

➤

tcycle n

tcycle n+1

➤

➤

VDDO

2

Qy

tjit(cc) = tcycle n –tcycle n+1

1000 Cycles

tsk(o)

CYCLE-TO-CYCLE JITTER

OUTPUT SKEW

nPCLK

PCLK

80ꢀ

tF

80ꢀ

20ꢀ

20ꢀ

Clock

Outputs

VDDO

2

tR

Q0:Q7,

QFB

t

PD

OUTPUT RISE/FALL TIME

PROPAGATION DELAY

nPCLK

PCLK

VOH

VOL

VDDO

2

Q0:Q7

QFB

Pulse Width

VOH

tPERIOD

VDDO

VO2L

FB_CLK

➤

t(Ø)

➤

tPW

odc =

tPERIOD

tjit(Ø) = t(Ø) — t(Ø) mean = Phase Jitter

(where t(Ø) is any random sample, and t(Ø) mean is the average

of the sampled cycles measured on controlled edges)

OUTPUT DUTY CYCLE/PULSE WIDTH/PERIOD

PHASE JITTER & STATIC PHASE OFFSET

86953BYI-147

www.icst.com/products/hiperclocks.html

REV. B APRIL 23, 2004

5

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]