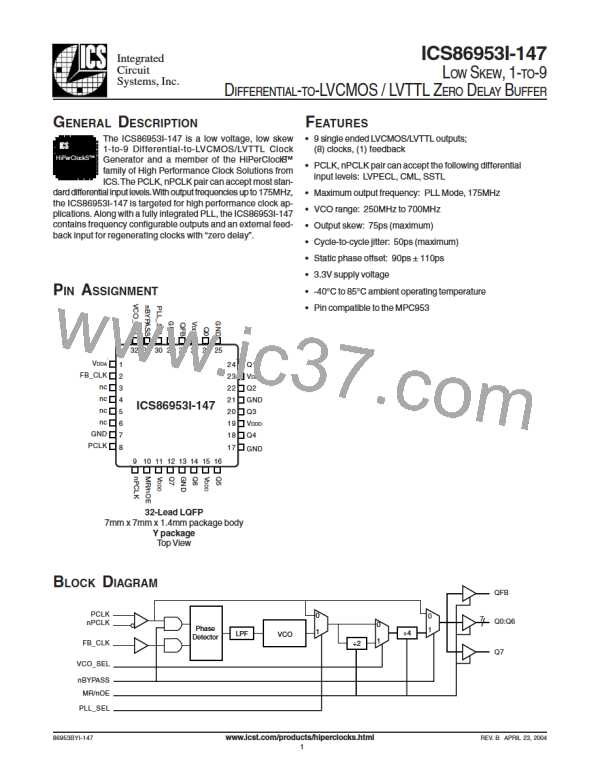

ICS86953I-147

Integrated

Circuit

Systems, Inc.

LOW

SKEW, 1-TO-9

D

IFFERENTIAL

-

TO-LVCMOS / LVTTL ZERO

DELAY

BUFFER

PACKAGE OUTLINE - Y SUFFIX FOR 32 LEAD LQFP

TABLE 8. PACKAGE DIMENSIONS

JEDEC VARIATION

ALL DIMENSIONS IN MILLIMETERS

BBA

SYMBOL

MINIMUM

NOMINAL

MAXIMUM

N

A

32

--

--

--

1.60

0.15

1.45

0.45

0.20

A1

A2

b

0.05

1.35

0.30

0.09

1.40

0.37

c

--

D

9.00 BASIC

7.00 BASIC

5.60 Ref.

9.00 BASIC

7.00 BASIC

5.60 Ref.

0.80 BASIC

0.60

D1

D2

E

E1

E2

e

L

0.45

0.75

θ

--

0°

7°

ccc

--

--

0.10

Reference Document: JEDEC Publication 95, MS-026

86953BYI-147

www.icst.com/products/hiperclocks.html

REV. B APRIL 23, 2004

11

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]