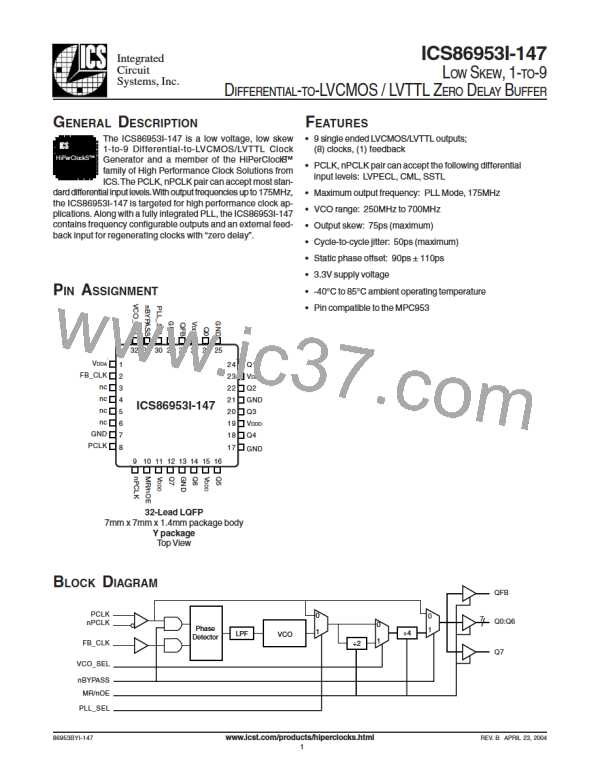

ICS86953I-147

Integrated

Circuit

Systems, Inc.

LOW

SKEW, 1-TO-9

D

IFFERENTIAL

-

TO-LVCMOS / LVTTL ZERO

DELAY

BUFFER

REVISION HISTORY SHEET

Description of Change

Added Pullup/Pulldown to Pin 9.

Pin Characteristics table - changed CIN limit from 4pF max. to 4pF typical.

Added 5pF min. and 7pF typical to CPD.

Updated Figure 3C and 3D.

Added Layout Guideline and PCB Board layout.

Pin Characteristics Table - added ROUT row.

Rev

B

Table

T1

T2

Page

2

2

Date

10/28/03

4/23/04

7

8 & 9

2

T2

B

86953BYI-147

www.icst.com/products/hiperclocks.html

REV. B APRIL 23, 2004

13

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]