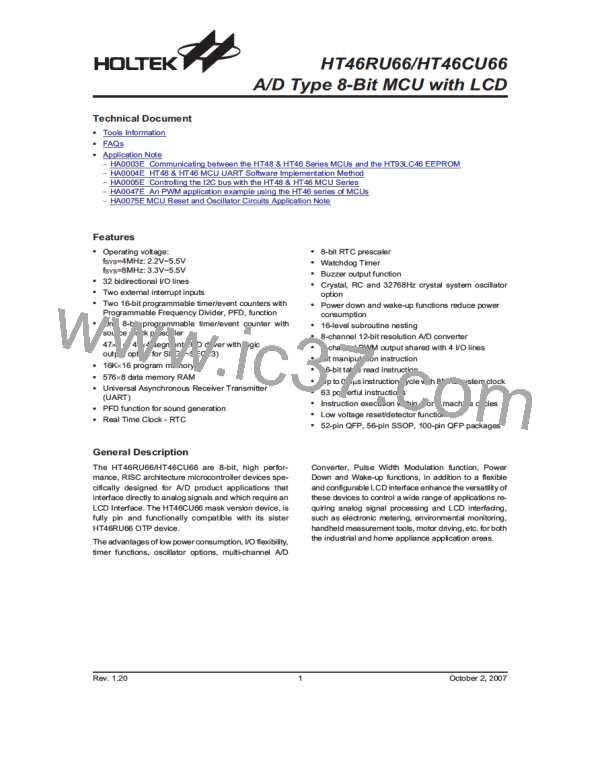

HT46RU66/HT46CU66

Bit No.

Label

Function

0~2

¾

Unused bit, read as ²0²

Defines the TMR1 active edge of the timer/event counter:

In Event Counter Mode (T1M1,T1M0)=(0,1):

1:count on falling edge;

3

T1E

0:count on rising edge

In Pulse Width measurement mode (T1M1,T1M0)=(1,1):

1: start counting on the rising edge, stop on the falling edge;

0: start counting on the falling edge, stop on the rising edge

4

5

T1ON

T1S

Enables/disables the timer counting (0=disable; 1=enable)

Defines the TMR1 internal clock source.

(0=fSYS/4; 1=32768Hz)

Defines the operating mode, T1M1, T1M0:

01=Event count mode (external clock)

10=Timer mode (internal clock)

11=Pulse width measurement mode

00=Unused

6

7

T1M0

T1M1

TMR1C (11H) Register

Bit No.

Label

Function

Defines the prescaler stages, T2PSC2, T2PSC1, T2PSC0=

000: fINT=fSYS

001: fINT=fSYS/2

010: fINT=fSYS/4

011: fINT=fSYS/8

100: fINT=fSYS/16

101: fINT=fSYS/32

110: fINT=fSYS/64

111: fINT=fSYS/128

0

1

2

T2PSC0

T2PSC1

T2PSC2

Defines the TMR2 active edge of the timer/event counter:

In Event Counter Mode (T2M1,T2M0)=(0,1):

1:count on falling edge;

3

T2E

0:count on rising edge

In Pulse Width measurement mode (T2M1,T2M0)=(1,1):

1: start counting on the rising edge, stop on the falling edge;

0: start counting on the falling edge, stop on the rising edge

4

5

T2ON

Enables/disables the timer counting (0=disable; 1=enable)

¾

Unused bit, read as ²0²

Defines the operating mode, T2M1, T2M0:

01=Event count mode (external clock)

10=Timer mode (internal clock)

11=Pulse width measurement mode

00=Unused

6

7

T2M0

T2M1

TMR2C (2EH) Register

Rev. 1.20

22

October 2, 2007

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]