DS2406

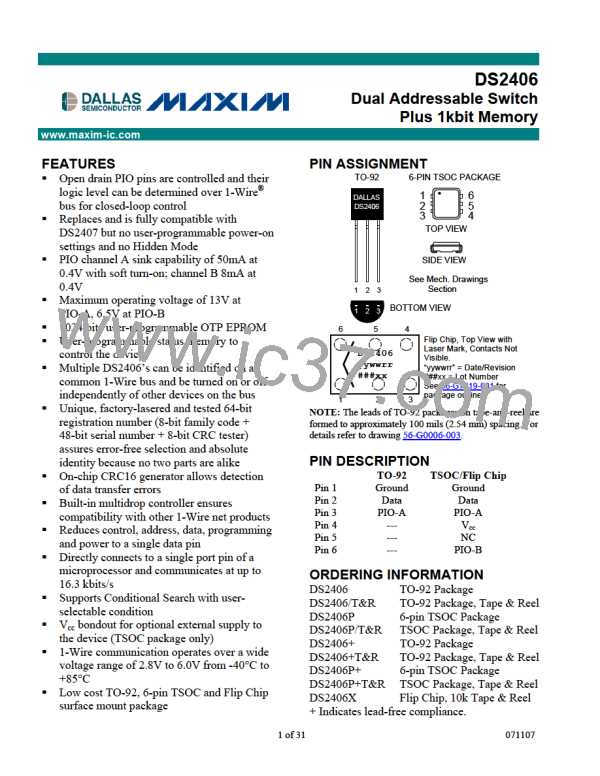

Memory Function Flow Chart (continued) Figure 7

From Figure 7

1st Part

To Figure 7

3rd Part

55h

Write Status

0Fh

Write Memory

N

N

?

?

Legend:

Y

Y

Bus Master TX

Bus Master TX

TA1(T7:T0), TA2 (T15:T8)

TA1(T7:T0), TA2 (T15:T8)

Decision made

by Bus Master

DS2406 sets Memory

Address = (T15:T0)

DS2406 sets Memory

Address = (T15:T0)

Decision made

by DS2406

Bus Master TX

Data Byte (D7:D0)

Bus Master TX

Data Byte (D7:D0)

Bus Master RX CRC16 of Command,

Address, Data (1st pass); CRC16 of

Address, Data (subsequent passes)

Bus Master RX CRC16 of Command,

Address, Data (1st pass); CRC16 of

Address, Data (subsequent passes)

N

N

N

CRC

Correct ?

CRC

Correct ?

S

R

Y

Y

Bus Master TX

Program Pulse

Address < 7

?

Bus Master

TX FFh or

Program Pulse

Y

DS2406 copies Scratch-

pad to Data EPROM

Bus Master TX

Program Pulse

DS2406 copies

Scratchpad to

Volatile Status

Bus Master RX Byte

from Data EPROM

DS2406 copies Scratch-

pad to Status EPROM

N

Y

EPROM

Byte Correct

?

Bus Master RX

Byte From

Volatile Status

Bus Master RX Byte

from Status EPROM

Y

End of

N

EPROM

Byte Correct

?

Data Mem.

?

Y

N

DS2406 increments

Address Counter

DS2406 increments

Address Counter

Bus Master TX

Reset Pulse

DS2406 TX

Presence Pulse

DS2406 loads new Address

into CRC Generator

DS2406 loads new Address

into CRC Generator

Vertical

Spare

11 of 31

DALLAS [ DALLAS SEMICONDUCTOR ]

DALLAS [ DALLAS SEMICONDUCTOR ]