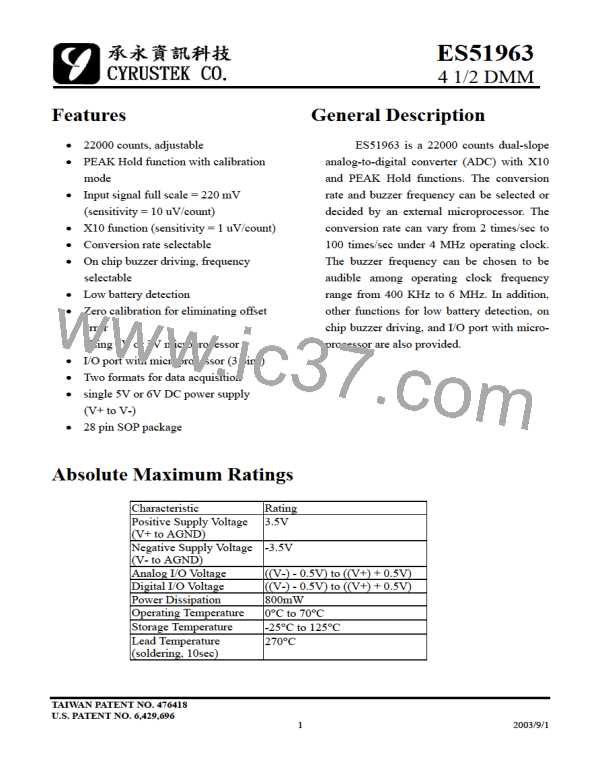

ES51963

4 1/2 DMM

For example, if the CR is 10 times/sec, the maximum DINT time is 44 ms, and the

resolution will be 22000 (11000) counts based on a 500 (250) kHz clock.

mode 2: ES51963 receives controlled status from microprocessor.

force A/D entering into AZ phase

(V-)+2.1V

(V-)+0.8V

EOC (O)

(520~1020)Tosc1

(1040~4096)Tosc1

T=(32~512)Tosc1

>4Tosc1

(V-)+2.1V

(V-)+0.8V

SCLK (I)

START

END

(0~256)Tosc1

512Tosc1

(2~1024)Tosc1

(2~1024)Tosc1

2C

uP

2E

(V-)+2.1V

(V-)+0.8V

STATUS (I/O) A/D

A/D

status

uP

520Tosc1

(4~256)Tosc1

O: output to microprocessor

I: input into IC

2D

2F

I/O: exchange between I and O

2A

2B

Note: 1. The START bit:

After time 2A, the EOC's state is forced to low (V-) and ES51963 enter

into AZ phase. And at the same time, STATUS is changed from output pin to

input pin with a 3 uA pull low current provided by ES51963 internally. Then

microprocessor can send control status to STATUS. It is suggested that micro-

processor begins to drive STATUS between 2B and 2C.

2. The END bit:

The microprocessor stopped driving STATUS between 2D and 2E, and

ES51963 will begin to drive STATUS after 2F.

3. Serial Data Format (STATUS):

In mode 2, only the status bits X10, PEAK, PCAL, ZERO, C0, C1, C2, B0,

B1, B2, FORMAT and TEST are meaningful. However the microprocessor still

needs to send the complete word of status (16 bits) although ES51963 will

discard the other bits.

4. The detail timing between SCLK and STATUS is as follow:

(32~512)Tosc1 with 40~60 % duty cycle

(V-) + 2.1V

(V-) + 0.8V

SCLK

(V-) + 2.1V

(V-) + 0.8V

STATUS

S0

S1

S2

S14 S15

12

2003/9/1

CYRUSTEK [ Cyrustek corporation ]

CYRUSTEK [ Cyrustek corporation ]