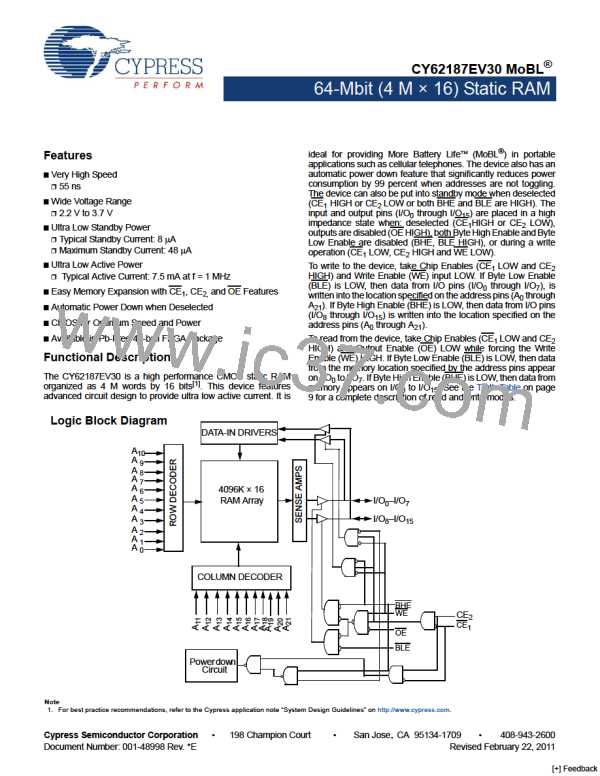

CY62187EV30 MoBL®

Switching Waveforms (continued)

Figure 8. Write Cycle 3 (WE Controlled, OE LOW)[25, 26]

tWC

ADDRESS

CE1

tSCE

CE2

tBW

BHE/BLE

WE

tAW

tHA

tSA

tPWE

tSD

tHD

DATA I/O

NOTE 26

VALID DATA

tLZWE

tHZWE

Figure 9. Write Cycle 4 (BHE/BLE Controlled, OE LOW)[25,26]

tWC

ADDRESS

CE1

CE2

tSCE

tAW

tHA

tBW

BHE/BLE

WE

tSA

tPWE

tSD

tHD

NOTE 26

VALID DATA

DATA I/O

Notes

25. If CE goes HIGH and CE goes LOW simultaneously with WE = V , the output remains in a high impedance state.

1

2

IH

26. During this period the I/Os are in output state and input signals should not be applied.

Document Number: 001-48998 Rev. *E

Page 9 of 14

[+] Feedback

CYPRESS [ CYPRESS ]

CYPRESS [ CYPRESS ]