CY62187EV30 MoBL®

Document History Page

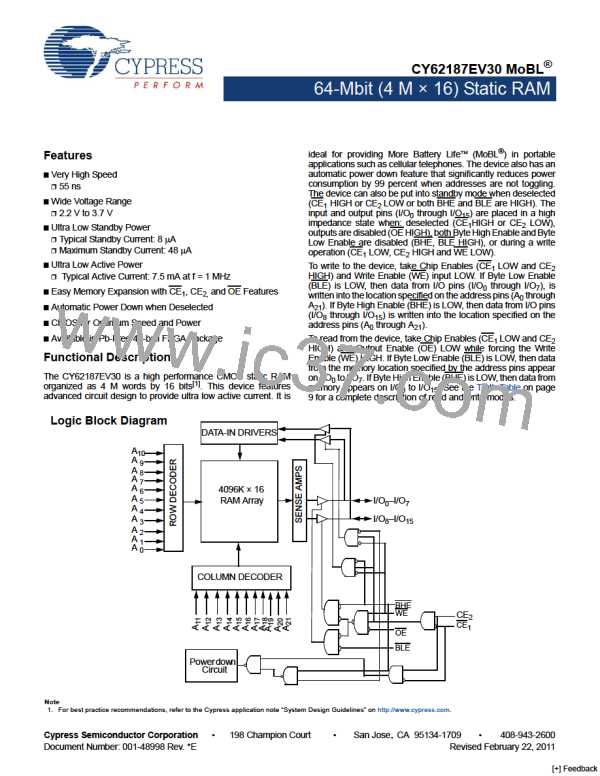

Document Title: CY62187EV30 MoBL® 64-Mbit (4 M × 16) Static RAM

Document Number: 001-48998

Orig. of

Change

Submission

Date

Revision

ECN

Description of Change

**

2595932 VKN/PYRS

2644442 VKN/PYRS

2672650 VKN/PYRS

10/24/08

01/23/09

03/12/09

New Datasheet

*A

*B

Updated the Package diagram on page 10

Extended the VCC range to 3.7V

Added 55 ns speed bin and it’s related information

Changed ICC (typ) from 2.5 mA to 3.5 mA at f = 1 MHz

Changed ICC (max) from 4 mA to 6 mA at f = 1 MHz

For 70 ns speed, changed ICC (typ) form 33 mA to 28 mA at f = fMAX

For 70 ns speed, changed ICC (max) from 40 mA to 45 mA at f = fMAX

For 70 ns speed, changed tPWE from 45 to 50 ns, tSD from 30 to 35 ns

Modified footnote #6

Changed 48-Ball FBGA package dimensions from 8 x 9.5 x 1.6 mm to

8 x 9.5 x 1.4 mm and updated package diagram on page 10

*C

2737164 VKN/AESA

07/13/09

Converted from preliminary to final

Changed ICC(typ) from 3.5 mA to 4 mA at f = 1 MHz

Changed ICC(typ) from 35 mA to 45 mA and from 28 mA to 35 mA for the speeds

50 ns and 70 ns respectively at f = fmax

Included VCC range in the test condition of the “Electrical Characteristics” table

for the specs VOH, VOL, VIH, VIL

Changed VIL(max) from 0.8V to 0.7V for VCC = 2.7V to 3.7V

Changed CIN spec from 20 pF to 25 pF and COUT spec from 20 pF to 35 pF

Included thermal specs for 48-FBGA

Included VCC range for VTH spec in the AC test load table

Changed tLZBE spec from 5 ns to 10 ns

Added footnote #20 related to chip enable

*D

*E

2765892

3177000

VKN

AJU

09/18/09

Removed 70 ns speed

For 55 ns speed, at f = 1 MHz, changed ICC (max) spec from 6 mA to 9 mA

Changed ICC(typ) from 4 mA to 7.5 mA at f = 1 MHz

02/18/2011 Updated Features (Corrected ICC(typ) from 4 mA to 7.5 mA).

Updated Pin Configuration (Renamed Figure 1 as “48-ball FBGA”).

Updated Product Portfolio (Corrected ICC(typ) from 4 mA to 7.5 mA).

Updated Electrical Characteristics (Included BHE and BLE in ISB2 test

conditions to reflect Byte power down feature).

Updated Table 1 on page 5 (AC Test Loads).

Updated Data Retention Characteristics (Included BHE and BLE in ICCDR test

conditions to reflect Byte power down feature, corrected tR(min) from tRC to

55 ns).

Added Ordering Code Definitions.

Updated Package Diagram.

Added Acronyms and Units of Measure.

Changed all instances of IO to I/O.

Updated in new template.

Document Number: 001-48998 Rev. *E

Page 13 of 14

[+] Feedback

CYPRESS [ CYPRESS ]

CYPRESS [ CYPRESS ]