Parallel Programming

Characteristics

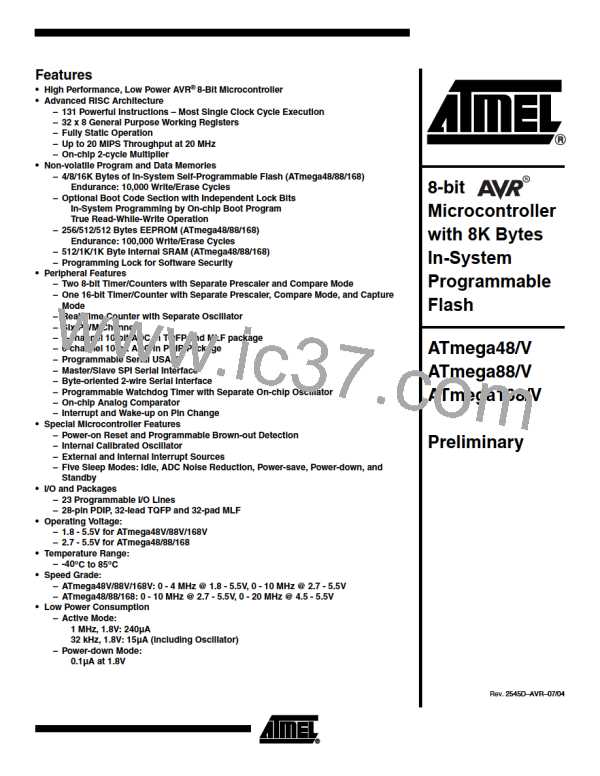

Figure 125. Parallel Programming Timing, Including some General Timing

Requirements

tXLWL

tXHXL

XTAL1

tDVXH

tXLDX

Data & Contol

(DATA, XA0/1, BS1, BS2)

tBVPH

tPLBX tBVWL

tWLBX

PAGEL

tPHPL

tWLWH

WR

tPLWL

WLRL

RDY/BSY

tWLRH

Figure 126. Parallel Programming Timing, Loading Sequence with Timing

Requirements(1)

LOAD DATA

LOAD ADDRESS

(LOW BYTE)

LOAD DATA

(LOW BYTE)

LOAD DATA

(HIGH BYTE)

LOAD ADDRESS

(LOW BYTE)

tXLPH

tXLXH

tPLXH

XTAL1

BS1

PAGEL

DATA

ADDR0 (Low Byte)

DATA (Low Byte)

DATA (High Byte)

ADDR1 (Low Byte)

XA0

XA1

Note:

1. The timing requirements shown in Figure 125 (i.e., tDVXH, tXHXL, and tXLDX) also apply

to loading operation.

284

ATmega48/88/168

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]