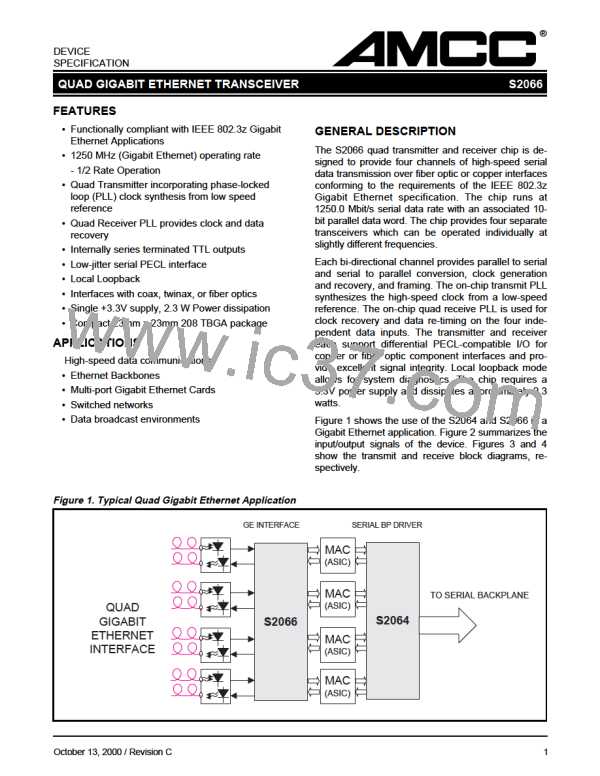

QUAD GIGABIT ETHERNET TRANSCEIVER

Serial to Parallel Conversion

S2066

Parallel Output Clock Rate

Once bit synchronization has been attained by the

S2066 CRU, the S2066 must synchronize to the 10

bit word boundary. Word synchronization in the

S2066 is accomplished by detecting and aligning to

the 8B/10B K28.5 codeword. The S2066 will detect

and byte-align to either polarity of the K28.5. Each

channel of the S2066 will detect and align to a K28.5

anywhere in the data stream. The presence of a

K28.5 is indicated for each channel by the assertion

of the COM_DETx (Comma Detect) signal.

Two output clock modes are supported. When

CMODE is HIGH, a complementary TTL clock at the

data rate is provided on the RBC1/0x outputs. Data

should be clocked on the rising edge of RBC1x.

When CMODE is LOW, the S2066 outputs a

complementary TTL clock at 1/2 the data rate in

compliance with the the Gigabit Ethernet Physical

Media Attachment (PMA) specification. Data should

be latched on the rising edge of RBC1x and the

rising edge of RBC0x.

If consecutive K28.5 characters are received, the

S2066 RBC1/0x clock operates without glitches or

loss of cycles.

Data Output

Data is output on the DOUTx[0:9] outputs. The

COM_DETx signal is used to indicate the reception

of a valid K28.5 character and is driven concurrent

with the K28.5 character on the DOUTx[0:9] outputs.

Table 4. Output Clock Modes

Mode

CMODE

RBC1/0x Freq.

62.5 MHz

The S2066 TTL outputs are optimized to drive 65Ω

line impedances. Internal source matching provides

good performance on unterminated lines of reason-

able length.

Half Clock Mode

Full Clock Mode

0

1

125 MHz

9

October 13, 2000 / Revision C

AMCC [ APPLIED MICRO CIRCUITS CORPORATION ]

AMCC [ APPLIED MICRO CIRCUITS CORPORATION ]