DESIGN EXAMPLES

We now apply these equations in the following

design examples.

EQUATIONS AND DERIVATIONS

Dual Slope Analog Processor equations and derivations

are as follows:

t

INT

.

.

1

V

t

(1)

REF DINT

∫

V

(t)dt =

IN

Design Example 1:

.

R

C

INT

0

INT

R

C

INT

INT

For V (t) = V (constant):

IN

IN

1. Pick resolution = 16 bit.

1

2. Pick t

= 4x

= 4 x 16.6667 msec.

= 66.6667ms

INT

.

V

t

1

.

REF DINT

60Hz

(2)

.

t

V

=

IN

INT

.

C

INT

R

.

C

INT

R

INT

INT

= 0.0666667 sec.

t

t

DINT

(2a)

(3)

.

. .

V

= V

REF

IN

3. Pick clock period = 1.08507 µs and number of counts

INT

0.0666667

= 61440

over t

=

INT

.

t

I

INT

B

-6

C

=

1.08507x10

INT

V

INT

4. Pick V MAX value, e.g., V MAX = 2.0 V

IN

I MAX = 20µA

IN

At V MAX, the current I is also at a maximum level,

IN

B

2.0

for a given R

value:

INT

R

INT

=

= 100 kΩ

B

-6

20x10

V

IN

I

B

V

MAX

IN

(4)

R

INT

=

=

5. Applying equation (3) to calculate C

-6

INT:

I MAX

B

C

INT

= (0.0666667)(20x10 )/4 where V

~

= 4.0V

INT

From equation (2a),

0.33 µF

=

.

V

t

IN INT

(5a)

(5b)

~

and C ≥ C : C C

REF AZ

= =

~

V

=

6. Pick C

0.33 µF

REF

REF

AZ

INT

= 133.3333 msec

t

DINT

OR

7. Pick t

= 2 x t

INT

DINT

.

t

V

MAX

IN

INT

MAX

V

=

REF

.

.

R

INT

V

INT

MAX

C

INT

t

DINT

8. Calculate V

=

V

REF

t

MAX

DINT

Rearranging equations (3) and (4):

.

-6

3

C

V

INT

4 x 0.33 x 10 x 100 x 10

INT

t

=

(6)

(7)

INT

=

V

-3

I

133.3333 x 10

B

and

V

MAX

IN

~

=

1.00V

I MAX =

B

R

INT

At V

V

MAX, equation (6) becomes:

INT = INT

.

Design Example 2:

1. Select resolution of 17 bit. Total number of

C

=

V

MAX

INT

INT

t

INT

(6a)

I MAX

B

counts during t

is131,072.

INT

Combining (6a) and (7):

.

.

R

INT

.

C

V

MAX

INT

INT

MAX

. .

(8)

t

=

2. We can pick t

of 16.6667 msec. x 5 = 83.3333 msec.

INT

INT

V

IN

In equation (5b), substituting equation (8) for t

or alternately, pick t

equal

INT

16.6667 msec. x 6 = 100.00 msec.

(for 60 Hz rejection)

:

INT

.

.

R

INT

C

INT

V

INT

MAX

which is t

= 20.00 msec. x 5

INT

.

V

MAX

V

MAX

IN

IN

(9)

= 100.00 msec. (for 50 Hz rejection)

V

=

=

REF

t

MAX

DINT

.

.

Therefore, using t

= 100 msec. would achieve

C

V

INT

MAX

MAX

R

INT

INT

INT

both 50 Hz and 60 Hz cycle noise rejection. For this

example, the following calculations would assume

t

DINT

t

of 100 msec. Now select period equal to

For t

MAX = 2 x t

,

INT

0.5425 µsec. (clock frequency of 1.8432 MHz)

DINT

INT

equation (9) becomes:

.

.

R

INT

C

V

MAX

INT

INT

2t

(10)

V

=

REF

INT

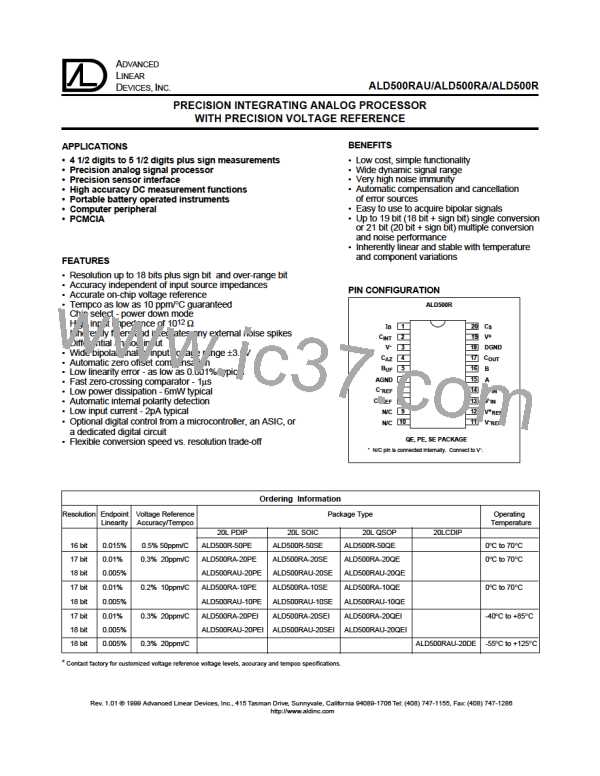

ALD500RAU/ALD500RA/ALD500R

Advanced Linear Devices

11

ALD [ ADVANCED LINEAR DEVICES ]

ALD [ ADVANCED LINEAR DEVICES ]