ASAHI KASEI

[AK4115]

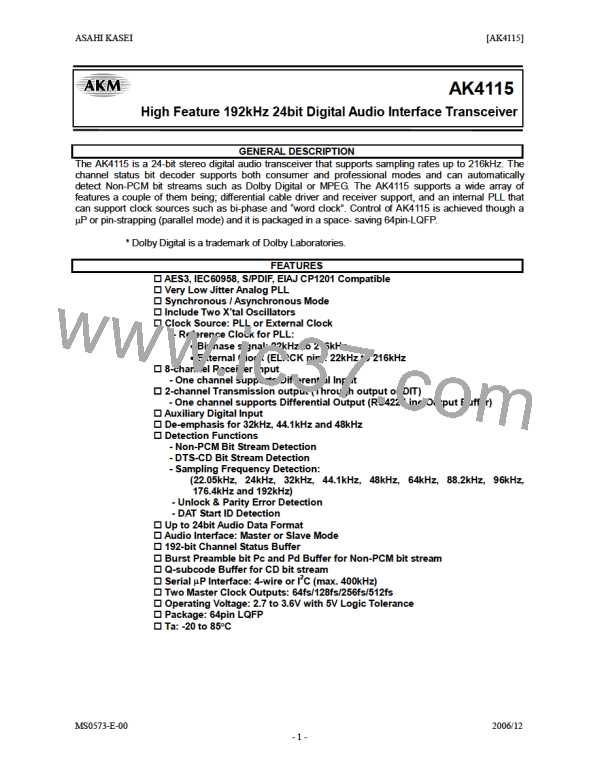

b. Serial mode & AES3 mode (P/SN pin = “L”, AES3 bit = “1”, ASYNC bit = “0”)

Block

Start

(B pin)

RX

TX

DIF1 BCU_IO

Channel

Status bit

Validity

bit

Channel

Status bit

Validity

bit

bit

bit

User bit

User bit

VOUT pin

VRX bit

SDTO pin

(Note 31)

VOUT pin

VRX bit

SDTO pin

(Note 31)

VOUT pin

VRX bit

SDTO pin

(Note 31)

VOUT pin

VRX bit

CR191-0 bits

SDTO pin

(Note 28)

C pin

CT191-0 bits

(Note 32)

VIN pin

VTX bit

(Note 34)

0

Input

Output

Input

SDTO pin

U pin

0

C pin

U pin

SDTO pin

(Note 30)

All

“0” data

VIN pin

VTX bit

(Note 35) (Note 34)

CR191-0 bits

SDTO pin

(Note 29)

1

0

1

CT191-0 bits

CR191-0 bits

SDTO pin

(Note 28)

CT191-0 bits

DAUX pin

(Note 33)

DAUX

pin

DAUX

pin

SDTO pin

1

C pin

U pin

SDTO pin

(Note 30)

CT191-0 bits

DAUX pin

(Note 33)

CR191-0 bits

SDTO pin

(Note 29)

DAUX

pin

DAUX

pin

Output

SDTO pin

(Note 31)

Note 28. Channel status bit for RX can be monitored by CR191-0 bits and SDTO pin.

Note 29. Channel status bit for RX can be monitored by C pin, CR191-0 bits and SDTO pin.

Note 30. User bit for RX can be monitored by U pin and SDTO pin.

Note 31. Validity bit for RX can be monitored by VOUT pin, VRX bit and SDTO pin.

Note 32. C pin and CT191-0 bits are ORed internally.

Note 33. Channel status bit can select either CT191-0 bits or DAUX pin by the setting of CTX bit.

Note 34. VIN pin and VTX bit are ORed internally.

Note 35. When UDIT bit is “1”, the recovered U bits are used for DIT(DIR-DIT loop mode of U bit).

Table 7. Block start, Channel Status bit, User bit and Validity bit in serial mode & AES3 mode

c. Parallel mode (P/SN pin = “H”)

Block

Start

(B pin)

RX

TX

Channel

Status bit

Validity

bit

User bit

Validity bit

VOUT pin

Channel Status bit User bit

Default value of

CT191-0 bits

All

Output

C pin

U pin

VIN pin

“0” data

Table 8. Block start, Channel Status bit, User bit and Validity bit in parallel mode

MS0573-E-00

2006/12

- 21 -

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]