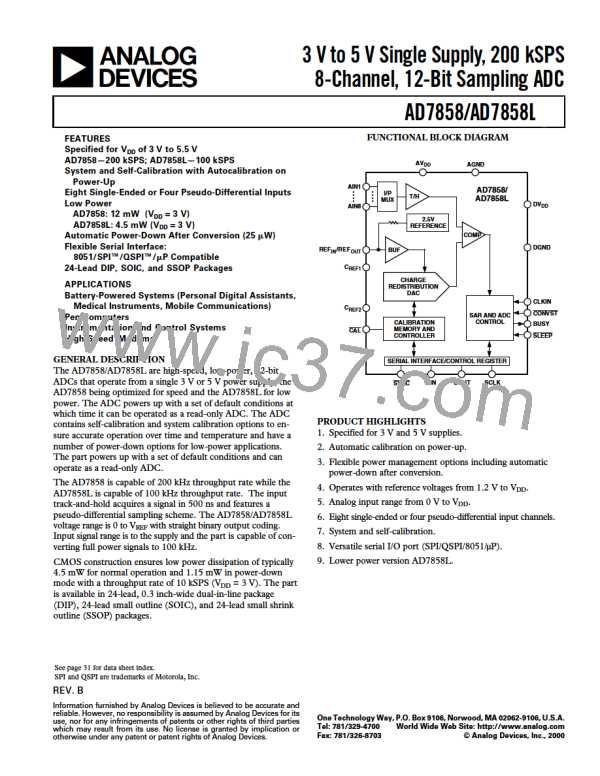

AD7858/AD7858L

Figure 27 shows a system gain calibration (assuming a system

full scale greater than the reference voltage) where the analog

input range has been increased after the system gain calibration

is completed. A system full-scale voltage less than the reference

voltage may also be accounted for by a system gain calibration.

system (gain + offset) calibrations will be sufficient. If the sys-

tem errors are large (close to the specified limits of the calibra-

tion range) three system (gain + offset) calibrations may be

required to reduced the offset and gain errors to at least the 12-

bit level. There will never be any need to perform more than

three system (offset + gain) calibrations.

MAX SYSTEM FULL SCALE

MAX SYSTEM FULL SCALE

The zero scale error is adjusted for an offset calibration and the

positive full-scale error is adjusted for a gain calibration.

IS ؎2.5% FROM V

IS ؎2.5% FROM V

REF

REF

SYS F.S.

SYS F.S.

V

– 1LSB

V

– 1LSB

REF

REF

System Calibration Timing

SYSTEM GAIN

CALIBRATION

ANALOG

INPUT

RANGE

ANALOG

INPUT

RANGE

The calibration timing diagram in Figure 29 is for a full system

calibration where the falling edge of CAL initiates an internal

reset before starting a calibration (note that if the part is in power-

down mode the CAL pulsewidth must take account of the power-up

time). If a full system calibration is to be performed in software

it is easier to perform separate gain and offset calibrations so

that the CONVST bit in the control register does not have to be

programmed in the middle of the system calibration sequence.

The rising edge of CAL starts calibration of the internal DAC

and causes the BUSY line to go high. If the control register is

set for a full system calibration, the CONVST must be used

also. The full-scale system voltage should be applied to the

analog input pins from the start of calibration. The BUSY line

will go low once the DAC and System Gain Calibration are

complete. Next the system offset voltage is applied to the AIN

pin for a minimum setup time (tSETUP) of 100 ns before the

rising edge of the CONVST and remain until the BUSY signal

goes low. The rising edge of the CONVST starts the system

offset calibration section of the full system calibration and also

causes the BUSY signal to go high. The BUSY signal will go

low after a time tCAL2 when the calibration sequence is com-

plete. In some applications not all the input channels may be

used. In this case it may be useful to dedicate two input chan-

nels for the system calibration, one which has the system offset

voltage applied to it, and one which has the system full scale

voltage applied to it. When a system offset or gain calibration is

performed, the channel selected should correspond to the sys-

tem offset or system full-scale voltage channel.

AGND

AGND

Figure 27. System Gain Calibration

Finally in Figure 28 both the system offset and gain are ac-

counted for by the a system offset followed by a system gain

calibration. First the analog input range is shifted upwards by

the positive system offset and then the analog input range is

adjusted at the top end to account for the system full scale.

MAX SYSTEM FULL SCALE

IS ؎2.5% FROM V

MAX SYSTEM FULL SCALE

IS ؎2.5% FROM V

REF

REF

V

+ SYS OFFSET

SYS F.S.

SYS F.S.

–1LSB

REF

V

REF

V

– 1LSB

REF

SYSTEM OFFSET

CALIBRATION

FOLLOWED BY

ANALOG

INPUT

RANGE

ANALOG

INPUT

RANGE

SYSTEM GAIN

CALIBRATION

SYS OFFSET

AGND

SYS OFFSET

AGND

MAX SYSTEM OFFSET

IS ؎5% OF V

MAX SYSTEM OFFSET

IS ؎5% OF V

REF

REF

Figure 28. System (Gain + Offset) Calibration

System Gain and Offset Interaction

The inherent architecture of the AD7858/AD7858L leads to an

interaction between the system offset and gain errors when a

system calibration is performed. Therefore, it is recommended

to perform the cycle of a system offset calibration followed by a

system gain calibration twice. Separate system offset and system

gain calibrations reduce the offset and gain errors to at least the

12-bit level. By performing a system offset CAL first and a

system gain calibration second, priority is given to reducing the

gain error to zero before reducing the offset error to zero. If the

system errors are small, a system offset calibration would be

performed, followed by a system gain calibration. If the system

errors are large (close to the specified limits of the calibration

range), this cycle would be repeated twice to ensure that the

offset and gain errors were reduced to at least the 12-bit level.

The advantage of doing separate system offset and system gain

calibrations is that the user has more control over when the

analog inputs need to be at the required levels, and the

CONVST signal does not have to be used.

The timing for a system (gain + offset) calibration is very similar

to that of Figure 29 the only difference being that the time tCAL1

will be replaced by a shorter time of the order of tCAL2 as the

internal DAC will not be calibrated. The BUSY signal will

signify when the gain calibration is finished and when the part is

ready for the offset calibration.

t1 = 100ns MIN, t14 = 50/90ns MIN 5V/3V,

t15 = 2.5 t

MAX, tCAL1 = 111114 t

,

CLKIN

CLKIN

tCAL2 = 13899 tCLKIN

t1

CAL (I/P)

t15

BUSY (O/P)

tCAL2

tCAL1

t16

Alternatively, a system (gain + offset) calibration can be

performed. It is recommended to perform three system (gain +

offset) calibrations to reduce the offset and gain errors to the

12-bit level. For the system (gain + offset) calibration priority is

given to reducing the offset error to zero before reducing the

gain error to zero. Thus if the system errors are small then two

CONVST (I/P)

tSETUP

V

V

OFFSET

AIN (I/P)

SYSTEM FULL SCALE

Figure 29. Timing Diagram for Full System Calibration

–22–

REV. B

ADI [ ADI ]

ADI [ ADI ]