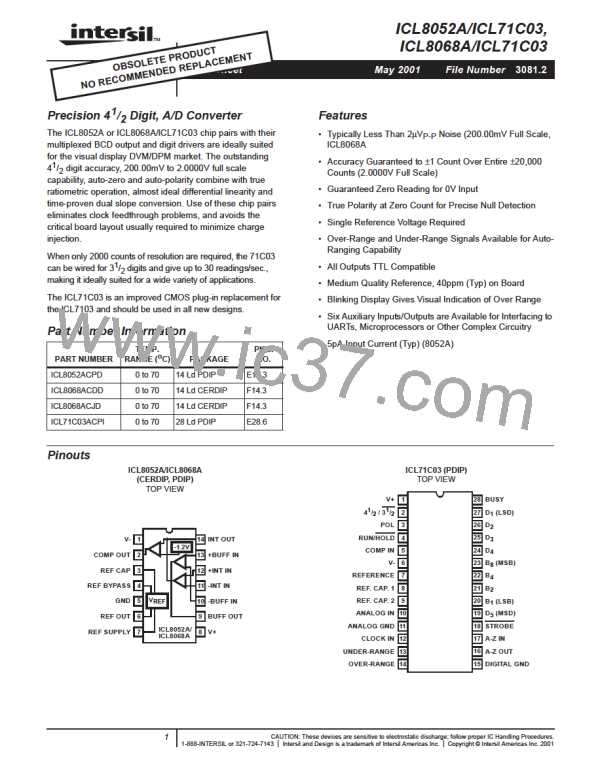

ICL8052A/ICL71C03, ICL8068A/ICL71C03

The auto-zero cap should be 1µF for all scales and the

Applications

reference capacitor should be 1µF times the gain of the

buffer amplifier. At this value if the input leakages of the

8052A/8068A are equal, the droop effects will cancel giving

zero offset. This is especially important at high temperature.

Specific Circuits Using the 8068A/71C03

8052A/A71C03

1

Figure 7 shows the complete circuit for a 4 / digit

2

( 200mV full scale) A/D converter with LED readout using

the internal reference of the 8068A/52A. If an external

reference is used, the reference supply (pin 7) should be

connected to ground and the 300pF reference cap deleted.

The circuit also shows a typical RC input filter. Depending on

Some typical component values are shown in Table 1. For

1

3 / digit conversion, use 12kHz clock.

2

V++ = +15V, V+ = 5V, V- = -15V

1

1

Clock Freq. = 120kHz (4 / Digit) or 12kHz (3 / Digit)

2

2

TABLE 1.

the application, the time-constant of this filter can be made

1

faster, slower, or the filter deleted completely. The / digit

2

SPECIFICATION

Full Scale V

VALUE

UNITS

mV

LED is driven from the 7-segment decoder, with a zero

20

200

10

2000

IN

reading blanked by connecting a D signal to RBI input of

5

Buffer Gain

(RB1 + RB2)

-----------------------------------

RB2

100

(See

Note)

1

V/V

the decoder.

A voltage translation network is connected between the

comparator output of the 8068A/52A and the auto-zero input

of the 71C03. The purpose of this network is to assure that,

during auto-zero, the output of the comparator is at or near the

threshold of the 71C03 logic (+2.5V) while the auto-zero

R

C

C

C

V

100

0.22

1.0

10

100

0.22

1.0

100

0.22

1.0

kΩ

µF

µF

µF

mV

µV

INT

INT

AZ

capacitor is being charged to V

(+100mV for a 200mV

REF

10

1.0

REF

REF

instrument). Otherwise, even with 0V in, some reference

integrate period would be required to drive the comparator

output to the threshold level. This would show up as an

equivalent offset error. Once the divider network has been

selected, the unit-to-unit variation should contribute less than

a tenth of a count error. A second feature is the back-to-back

diodes, used to lower the noise. In the normal operating mode

they offer a high impedance and long integrating time

constant to any noise pulses charging the auto-zero cap. At

startup or recovery from an overload, their impedance is low

to large signals so that the cap can be charged up in one

auto-zero cycle. The buffer gain does not have to be set

precisely at 10 since the gain is used in both the integrate and

deintegrate phase. For scale factors other then 200mV the

gain of the buffer should be changed to give a 2V buffer

output. For 2.0000V full scale this means unity gain and for

20,000mV (1µV resolution) a gain of 100 is necessary. Not all

8068As can operate properly at a gain of 100 since their offset

should be less than 10mV in order to accommodate the auto-

zero circuitry. However, for devices selected with less than

10mV offset, the noise performance is reasonable with

approximately 1.5µV near full scale. On all scales less than

200mV, the voltage translation network should be made

adjustable as an offset trim.

10

100

10

1000

100

1

Resolution (4 / Digit)

1

2

NOTE: Comment on offset limitations above. Buffer gain does not

improve ICL8052A noise performance adequately.

12

ETC [ ETC ]

ETC [ ETC ]