Data Sheet

June 1999

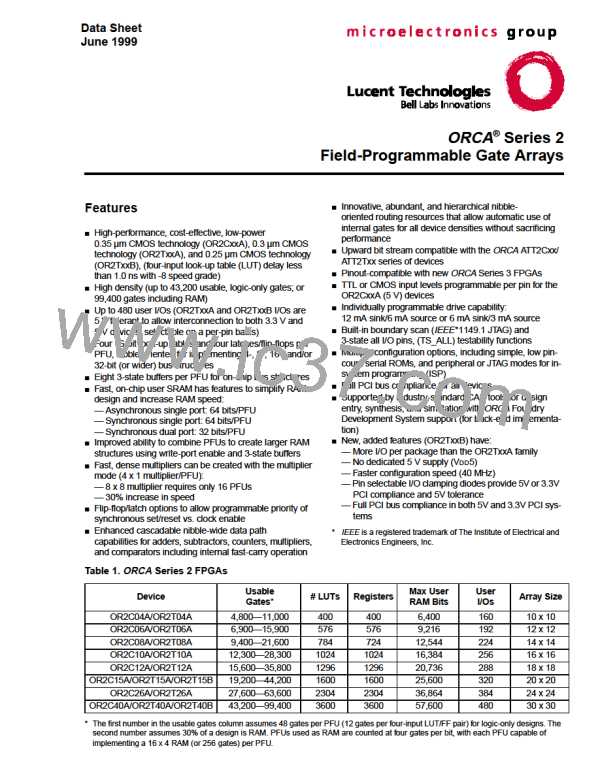

ORCA Series 2 FPGAs

.Timing Characteristics (continued)

Table 46B. OR2TxxB Programmable I/O Cell Timing Characteristics

OR2TxxA Commercial: VDD = 3.0 V to 3.6 V, 0 °C ≤ TA ≤ 70 °C; OR2TxxA Industrial: VDD = 3.0 V to 3.6 V, –40 °C ≤ TA ≤

+85 °C.

Speed

Parameter

Symbol

-7

-8

Unit

Min

Max

Min

Max

Inputs (TJ = 85 °C, VDD = min)

Input Rise Time

TR

TF

—

—

—

—

—

500

500

1.1

3.3

6.6

—

—

—

—

—

500

500

1.0

2.4

6.1

ns

ns

ns

ns

ns

Input Fall Time

PAD_IN_DEL

CHIP_LATCH

—

Pad to In Delay

Pad to Nearest PFU Latch Output

Delay Added to General Routing

(input buffer in delay mode for

OR2T15B and smaller devices)

—

—

—

—

—

—

8.9

6.4

8.7

—

—

—

8.2

6.0

8.0

ns

ns

ns

Delay Added to General Routing

(input buffer in delay mode for

OR2T40B)

Delay Added to Direct-FF Routing

(input buffer in delay mode for

OR2T15B and smaller devices)

Delay Added to Direct-FF Routing

(input buffer in delay mode for

OR2T40B)

Outputs (TJ = 85 °C, VDD = min, CL = 50 pF)

PFU CK to Pad Delay (DOUT[3:0] to

PAD):

Fast

Slewlim

Sinklim

DOUT_DEL(F)

DOUT_DEL(SL)

DOUT_DEL(SI)

—

—

—

2.8

3.6

8.3

—

—

—

2.5

3.3

8.0

ns

ns

ns

Output to Pad Delay (OUT[3:0] to

PAD):

Fast

Slewlim

Sinklim

OUT_DEL(F)

OUT_DEL(SL)

OUT_DEL(SI)

—

—

—

2.8

3.6

8.3

—

—

—

2.5

3.3

8.0

ns

ns

ns

3-state Enable Delay (TS[3:0] to

PAD):

Fast

Slewlim

Sinklim

TS_DEL(F)

TS_DEL(SL)

TS_DEL(SI)

—

—

—

3.0

3.8

9.1

—

—

—

2.7

3.4

8.7

ns

ns

ns

Notes:

If the input buffer is placed in delay mode, the chip hold time to the nearest PFU latch is guaranteed to be 0 if the clock is routed using the

primary clock network; (TJ = all, VDD = all). It should also be noted that any signals routed on the clock lines or using the TRIDI buffers directly

from the input buffer do not get delayed at any time.

The delays for all input buffers assume an input rise/fall time of ≤1 V/ns.

Lucent Technologies Inc.

157

ETC [ ETC ]

ETC [ ETC ]