Data Sheet

June 1999

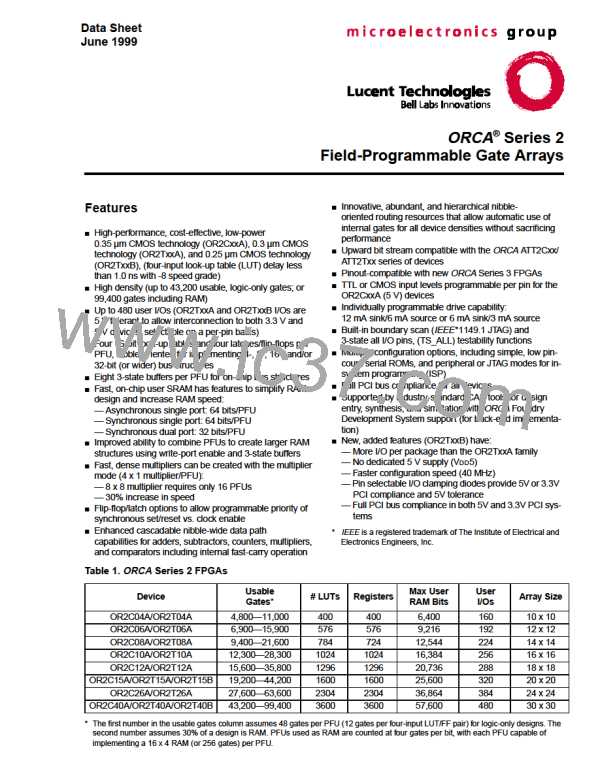

ORCA Series 2 FPGAs

Timing Characteristics (continued)

Table 43B. OR2TxxB Global Clock to Output Delay (Pin-to-Pin)—Output on Same Side of the Device as the

Clock Pin

OR2TxxB Commercial: VDD = 3.0 V to 3.6 V, 0 °C ≤ TA ≤ 70 °C;

Industrial: VDD = 3.0 V to 3.6 V, –40 °C ≤ TA ≤ +85 °C; CL= 50 pF.

Speed

Description

(TJ = 85 °C, VDD = min)

Device

-7

-8

Unit

Min

Max

Min

Max

CLK Input Pin → OUTPUT Pin

(Fast)

OR2T15B

OR2T40B

—

—

7.3

7.5

—

—

6.6

6.6

ns

ns

CLK Input Pin → OUTPUT Pin

(Slewlim)

OR2T15B

OR2T40B

—

—

8.2

8.4

—

—

7.4

7.6

ns

ns

CLK Input Pin → OUTPUT Pin

(Sinklim)

OR2T15B

OR2T40B

—

—

12.9

13.1

—

—

12.1

12.3

ns

ns

Notes:

The pin-to-pin timing information from ORCA Foundry version 9.2 and later is more accurate than this table. For earlier versions of ORCA Foundry,

the pin-to-pin timing parameters in this table should be used instead of results reported byORCA Foundry.

This clock delay is for a fully routed clock tree that uses the primary clock network. It includes both the input buffer delay,the clock routing to the

PFU CLK input, the clock→Q of the FF, and the delay through the output buffer. The delay will be reduced if any of the clock branches are not

used. The given timing requires that the input clock pin be located at one of the four center PICs on any side of the device and that the direct

FF→I/O routing be used.

If the clock pin is not located at one of the four center PICs, this delay must be increased by up to the following amounts:

OR2T15B = 5.7%, OR2T40B = 12.5%.

D

Q

OUTPUT (50 pF LOAD)

CLK

5-4846(F)

Figure 62. Global Clock to Output Delay

Lucent Technologies Inc.

151

ETC [ ETC ]

ETC [ ETC ]