MVTX2801

Data Sheet

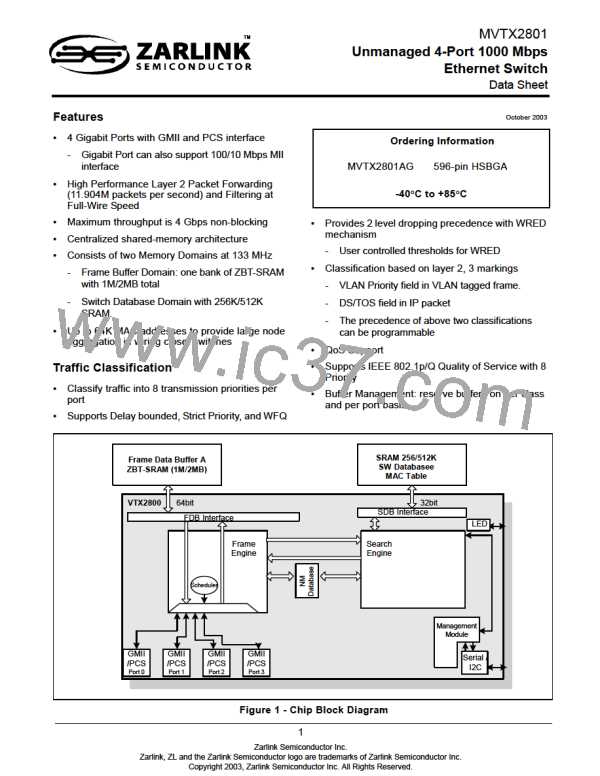

11.0 BGA and Ball Signal Description

11.1 BGA Views (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

AVDD

NC9

SCAN_EN

NC7

S_CLK

B_A[16] B_A[12]

B_A[17] B_A[13]

B_A[7]

B_A[8]

B_A[2]

B_A[3]

B_A[5]

B_OE#

B_D[27] B_D[26]

DEV_CFG

NC4

NC5

NC3

A

B

C

D

E

F

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VSS

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VSS

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

DEV_CF[

0]

LA_D[0]

B_WE# B_D[30]

B_D[25]

NC

NC

NC

[1]

LA_D[1] LA_CLK LA_D[3]

LA_D[2] LA_D[5] LA_D[9]

NC6

B_A[18] B_A[14] B_A[11]

B_A[4]

NC2

B_D[28]

AVDD

B_CLK B_D[22]

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC8

B_A[9]

B_A[6]

B_A[10] B_ADSC#

B_D[29] B_D[24] B_D[18] B_D[21]

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

LA_D[8] LA_D[7] LA_D[6] LA_D[4]

AGND

LB_A[20] B_A[15]

B_D[31]

VSS

AGND

VSS

B_D[17] B_D[23] B_D[19] B_D[16] B_D[14]

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

LA_D[10] LA_D[11] LA_D[12] LA_D[13] LA_D[14]

LA_D[15] LA_D[16] LA_D[19] LA_D[18] LA_D[17]

LA_D[20] LA_D[21] LA_D[22] LA_D[29] LA_D[24]

VSS

VDD

VDD

VDD

VCC

VCC

VCC

VSS

VCC

VCC

VCC

VDD

VDD

NC1

B_D[9]

B_D[4]

B_D[8]

P_A[1]

B_D[10] B_D[11] B_D[12]

VDD

B_D[20]

B_D[15]

B_D[3]

P_INT#

P_A[2]

B_D[6]

B_D[1]

P_WE#

B_D[7]

B_D[2]

P_RD#

G

H

LA_D[23] LA_D[25] LA_D[26] LA_D[27] LA_D[31]

LA_D[28] LA_D[30] LA_CS0# LA_D[37] LA_D[33]

VDD

VDD

VDD

VDD

B_D[13]

B_D[5]

J

P_D[15] P_D[11] P_D[12] P_D[13]

K

LA_CS1# LA_RW# LA_D[32] LA_D[46] LA_D[41]

LA_D[34] LA_D[35] LA_D[36] LA_D[53] LA_D[48]

P_CS#

P_A[0]

P_D[6]

P_D[14]

B_D[0]

P_D[9]

P_D[7]

P_D[3]

P_D[0]

P_D[8]

P_D[4]

P_D[1]

P_D[10]

P_D[5]

P_D[2]

L

VCC

VCC

M

LA_D[38] LA_D[40] LA_D[42] LA_D[61] LA_D[56]

LA_D[43] LA_D[44] LA_D[45] LA_A[4] LA_D[39]

LA_D[49] LA_D[50] LA_D[51] LA_D[52] LA_D[47]

LA_D[58] LA_D[57] LA_D[55] LA_D[54] LA_A[7]

LA_D[63] LA_D[62] LA_D[60] LA_D[59] LA_A[11]

LA_A[6] LA_A[5] LA_A[3] LA_A[14] LA_A[18]

VCC

VCC

VSS

VSS

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC

VCC

VSS

VSS

VCC

VCC

N

P

R

T

T_D[15] T_D[11] T_D[12] T_D[13] T_D[14]

T_D[10]

T_D[6]

T_D[5]

T_D[4]

T_D[7]

T_D[2]

T_D[8]

T_D[1]

T_D[9]

T_D[0]

S_RST# T_D[3] TMODE[1] TMODE[0] RESOUT#

G7_RX_E

U

V

NC[7]

NC[3]

NC[6]

LESYNO# LE_CLK0 LE_DO

R

G0_TXD[

G7_RX_D

LA_A[10] LA_A[9] LA_A[8] LA_A[20]

1]

VCC

VCC

NC[1]

NC[6]

NC[2]

NC[5]

NC[0]

W

Y

V

G0_CRS/ G0_TXD[4

G7_TX_E

N

LA_A[15] LA_A[13] LA_A[12]

NC[4]

L

]

G0_TXD[

7]

G7_RXCL MIITXCK[

LA_A[19] LA_A[17] LA_A[16] GREFC[0]

VDD

VDD

VDD

VDD

NC[0]

NC[7]

NC[3]

G7_COL

NC[7]

A A

A B

K

7]

MIITXCK[ G0_TXD[2G0_TXD[0 G0_TXCL G0_TX_E

0]

G7_TX_E

R

NC[5]

NC[4]

]

]

K

R

G0_RXCL G0_TXD[5G0_TXD[3 G0_RXD[ G0_RXD[

G7_CRS/

L

NC[2]

NC[0]

NC[7]

NC[4]

NC

NC[2]

NC[1]

NC

A C

A D

A E

K

]

]

2]

6]

G0_RXD[ G0_TX_E

G0_TXD[6 G0_RX_D

G7_TXCL

K

G0_COL

VSS

VSS

VDD

VSS

NC

NC

0]

N

]

V

G0_RXD[ G0_RXD[ G0_RXD[ G0_RXD[ G1_TXD[

VDD

VDD

VDD

VCC

VCC

VCC

VSS

VSS

VCC

VCC

VCC

VDD

VDD

VSS

NC[6]

NC[5]

NC[3]

NC[1]

5]

4]

3]

1]

0]

G0_RXD[ G0_RX_E

G1_RXD[ G1_RXD[ G1_RXD[ G2_TXD[0 G2_TXD[7 G2_RXD[ G2_RXD[ G2_RXD[ G3_TXD[1 G3_TXD[6

G3_RXD[ G3_RXD[

G3_RXD[ G3_RX_E

GREFC[1]

G3_COL

IND_CM

NC

NC[3]

NC[5]

NC

NC[1]

NC[6]

NC

NC[4]

NC[7]

NC

NC[2]

NC

NC[4]

NC[5]

NC[3]

NC[6]

NC[7]

24

NC[5]

NC[1]

NC[3]

NC

NC

NC[6]

NC[4]

NC[1]

NC

NC

NC

NC

NC[5]

NC

A F

A G

A H

A J

7]

R

2]

5]

7]

]

]

2]

4]

5]

]

]

3]

6]

4]

R

G1_TXD[1 G1_TXCL

G1_TXD[7 G2_TXCL G1_RXD[ G2_TXD[4 G2_TXD[3 G2_RXD[ G2_RXCL G2_RXD[ G2_RX_E G3_TX_E G3_RXD[ G3_RXD[ G3_RXD[

MIITXCK[

5]

G1CRS/L

M_MDIO

NC[1]

NC[3]

NC[6]

NC[4]

NC[7]

27

]

K

]

K

4]

]

]

3]

K

7]

R

N

0]

5]

7]

G1_TXD[2 G1_TXD[3 MIITXCK[ G1_RXD[ G1_RXCL

MIITXCK[ G2_TX_E G2_RXD[ G2_RX_D G3_TXCL G3_TXD[3 G3_TXD[5 G3_RXCL G3_RXD[ G3_RX_D

G2CRS/L

NC

NC[4]

NC[5]

NC[6]

NC[7]

NC

NC

NC

NC[0]

NC[2]

25

NC[2]

NC

]

]

1]

0]

K

2]

N

1]

V

K

]

]

K

2]

V

G1_TXD[5 G1_TXD[4 G1_TX_E

G1_RXD[

6]

G2_TXD[2 G2_TXD[6 G2_RXD[ G2_RXD[

G3_TXD[2 MIITXCK[ G3_TX_E G3_RXD[

GREFC[3] M_MDC

G1_COL

GREFC[2]

NC[0]

NC[0]

NC[2]

20

NC

NC

NC[0]

NC[1]

23

NC[0]

NC

]

]

R

]

]

0]

6]

]

3]

R

1]

G1_TXD[6 G1_TX_E G1_RXD[ G1_RXD[ G1_RX_D G1_RX_E G2_TXD[1 G2_TXD[5 G2_TX_E

G3_CRS/ G3_TXD[0 G3_TXD[4 G3_TXD[7

MIITXCK[

4]

MIITXCK[

6]

G2_COL

CM_CLK G4CRS/L NC[2]

NC[3]

21

NC

NC

NC

]

N

1]

3]

V

R

]

]

R

L

]

]

]

A K

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

22

26

28

29

30

Figure 5 - BGA Diagram

74

Zarlink Semiconductor Inc.

ZARLINK [ ZARLINK SEMICONDUCTOR INC ]

ZARLINK [ ZARLINK SEMICONDUCTOR INC ]