R

Platform Flash In-System Programmable Configuration PROMs

Revision

Date

Version

12/29/05

(Cont’d)

2.8

•

Notes for Figure 6, page 16, Figure 7, page 17, Figure 8, page 18, Figure 9, page 19, Figure 10,

page 20, Figure 11, page 21, Figure 12, page 22, and Figure 13, page 23 updated to specify the

need for a pull-up resistor if CF is not connected to PROGB.

•

•

•

Enhanced description under section "CLKOUT," page 8.

Enhanced description on design revision sampling under section "Design Revisioning," page 8.

Figure 4 and Figure 5 renamed to Table 7, page 8 and Table 8, page 8 respectively. All tables,

figures, and table and figure references renumber this point forward.

•

•

Value for "ICCINT," page 15 updated from 5mA to 1mA for XCFxxP.

Block diagram in Figure 2, page 2 updated to show clock source muxing and route clocking to all

functional blocks.

05/09/06

12/08/06

2.9

•

•

Added Virtex-5 LX support to Table 2.

"VIL" maximum for 2.5V operation in "Recommended Operating Conditions," page 14 updated

to match LVCMOS25 standard.

2.10

•

•

•

Added Virtex-5 LXT support to Table 2.

Defined reprogramming operation requirements in "Programming," page 3.

Corrected statements regarding the FPGA BUSY pin and corrected various references.

02/01/07

2.11

•

•

•

Removed Spartan-3L support and added Spartan-3A and Virtex-5 SXT support to Table 2.

Corrected Spartan-3E bitstream sizes in Table 2.

Correct supported voltages for "VCCJ" in Table 12, page 24, "VCCO" and "VCCJ" in Table 13,

page 26.

03/30/07

01/28/08

2.11.1

2.12

Added Spartan-3A DSP support to Table 2.

•

•

•

Added support for XC5VLX155, XC5VLX20T, and XC5VLX155T.

Updated JTAG TAP timing specifications in Table 9, page 7 to reflect improved performance.

Tied FPGA CS_B and FPGA RDWR_B to GND in the FPGA SelectMAP schematics to ensure

valid logic Low.

•

•

Hardwired external oscillator to FPGA CCLK in the FPGA slave mode schematics.

Added marking templates (Figure 14, page 31, Figure 15 and Figure 16), and corrected marks

for 48-pin TFBGA packages in "Marking Information," page 30.

•

•

•

Other edits and updates made.

Updated document template.

Updated URLs.

03/31/08

04/03/08

2.13

•

•

•

Added Virtex-5 FX FPGA support to Table 2.

Corrected markings for all packaging (Figure 14, page 31, Figure 15, and Figure 16).

Added note regarding variances in packaging and marking to Page 31.

2.13.1

•

•

Corrected typo.

Updated trademark notations.

05/14/08

07/07/08

11/14/08

10/26/09

2.14

2.15

2.16

2.17

Added support for XC5VSX240T and Platform Flash XL to Table 2.

Updated "Write Protection," page 4.

Added Virtex-5 TXT FPGA to Table 2.

•

•

Globally changed PROG_B and PROGRAM to PROGRAM_B.

Removed the following information from this data sheet to UG161, Platform Flash PROM User

Guide:

•

•

•

Table 2 entitled “Xilinx FPGAs and Compatible Platform Flash PROMs”

Section entitled “PROM to FPGA Configuration Mode and Connections Summary”

Section entitled “Configuration PROM-to-FPGA Device Interface Connection Diagrams”

•

•

•

•

Moved “up to 33 MHz” from FPGA Configuration Interface bullets in "Features," page 1 to

"Description," page 1, and added reference to related considerations.

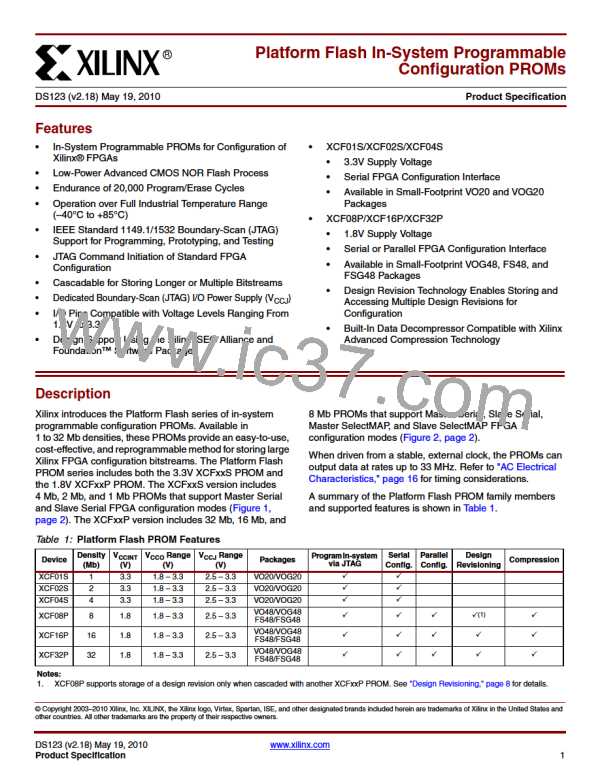

Table 1, page 1: Changed lower bound on VCCO for XCF08P, XCF16P, and XCF32P devices

from 1.5V to 1.8V. Added table note 1 about design revisioning for the XCF08P.

Added statement about ignoring non-JTAG input pins to second paragraph of "In-System

Programming," page 3.

Added reference to Platform Flash PROM User Guide in "External Programming," page 3 and

"Internal Oscillator," page 8.

DS123 (v2.18) May 19, 2010

www.xilinx.com

Product Specification

34

XILINX [ XILINX, INC ]

XILINX [ XILINX, INC ]