W83759A

Control Signal

IDE ATA Bus x 2

IDEIOR, IDEIOW

IORDY

IDEIOR, IDEIOW

VL_IDE

W83759AF

(100-pin)

LADS, ... *

IO Device

XIOR

LDEV, LRDY

XIOW

RDYRTN

CPU

XIOR

XIOR

XIOW

Super IO

W83787F

(100-pin)

VL-Bus

Chip Set

W83C491/492

(160-pin x2)

LADS,...

LDEV, LRDY

RDYRTN

XIOW

VL_BUS

ISA Bus

* LADS,... = LADS, HMIO, HWR, HDC, BE2, BE0

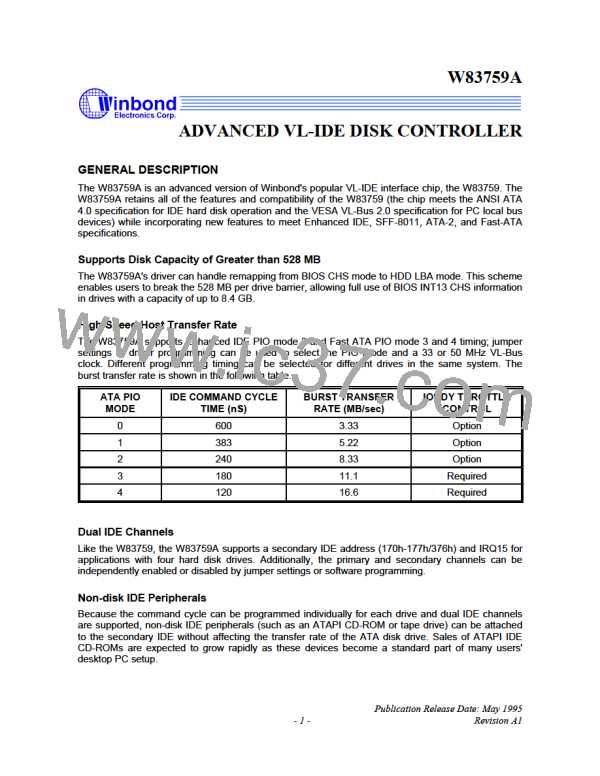

FUNCTION BLOCK DIAGRAM

LCLK

SYSRST

LADS

LRDY

LDEV

TIMING

REGISTERS

MUX

CONTROL

LOGIC

RDYRTN

SP1, MD1, MD0

Command

Enable

16

Bit

1f0 32

/170

Bit

IORDY

HA[9:2]

IDEA[2:0]

DECODE

LOGIC

BE2, BE0

SA1, SA0, AEN

IDE0CS1

IDE0CS0

IDE1CS1

IDE1CS0

IDEIOR

HMIO, HWR, HDC

VGAOEH, VGAOEL

PREFETCH

CONTROL

XIOR, XIOW

IDEIOW

Data Flow

Control

ID[15:0]

SD[7:0]

DATA

BUFFER

HD[31:0]

Publication Release Date: May 1995

Revision A1

- 27 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]