W83759A

FUNCTIONAL DESCRIPTION

Reset Initialization

The CPU clock rate, hard disk access time, hard disk controller enable, and hard disk I/O select are

latched at the rising edge of SYSRST . These values are used to control the host and drive access

signal timing. Additionally, the W83759A is initialized to a known state by an active low on SYSRST.

Any operation in progress is immediately terminated by SYSRST .

Host in Terface

The W83759A operates as a slave device, responding only to cycles within the host I/O address

space. The IDE drive data port at address 1F0h (170h) is a 16-bit port that requests a double-word

data transfer at address 1F0h (170h). All byte swapping, conversion, word, and double-word assembly

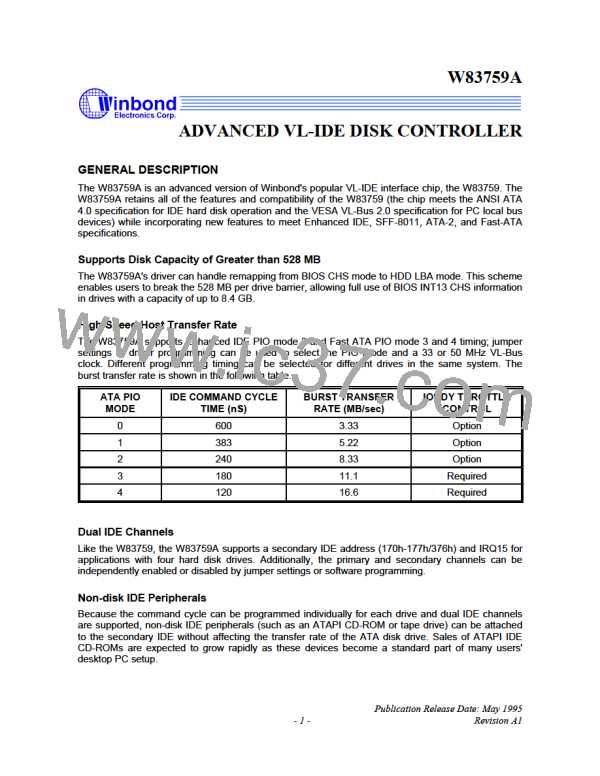

are done at the host interface. Table 1 summarizes the W83759A host interface cycle decoding.

Table 1. W83759A Cycle Definition

ADDRESS SPACE

HOST BUS

CYCLE

W83759A CYCLE

HMIO

HDC

HWR

0

0

0

0

1

1

1

1

0

1

0

1

I/O Read

I/O Write

I/O Read

I/O Write

IDE0 Read Cycle

IDE0 Write Cycle

IDE1 Read Cycle

IDE1 Write Cycle

1F0h- 1F7h and 3F6h

1F0h- 1F7h and 3F6h

170h- 177h and 376h

170h- 177h and 376h

a. CPU WRITE CYCLES

Table 2. W83759A Write Data Operation

BYTE ENABLE

W83759A INPUT DATA

I/O ADDRESS

HD[31:16]

HD[15:0] SD[7:0]

BE3

1

BE2

1

BE1

1

BE0

0

Valid

Valid

Valid

Valid

´

´

´

1F1- 1F7 (171- 177)

1

1

0

1

´

´

1

0

1

1

´

´

0

1

1

1

´

´

´

1

1

0

0

Valid

Valid

1F0 (170)

0

0

0

0

Valid

´

8-bit IDE Write Data Path:

CPU ® Valid HD Byte ® SD[7:0] ® W83759A ® ID[7:0]

16/32-bit IDE Write Data Path:

CPU ® Valid HD Word ® W83759A ® ID[15:0]

- 28 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]