Preliminary W78E378/W78C378/W78C374

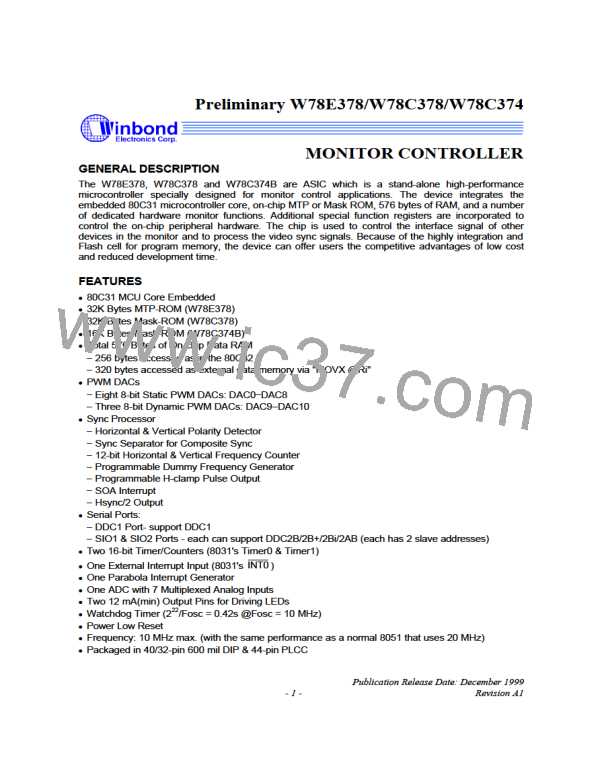

DDC1/SIO1 and SIO2 Ports

1. DDC1/SIO1 port

DDC Port

IN

SIO1

SCL

SDA

SCL

OUT

IN

SDA

OUT

0

1

Support DDC2B/2B+

DDC1

OUT

SDA

SCL

Vsync

Support DDC1

ENDDC1

· ENDDC1 = 1, used as DDC1 (Display Data Channel) port:

To support DDC1, use Vsync signal for shift clock and P3.0 (SDA) for data output.

·

ENDDC1 = 0, used as SIO1 port:

To support DDC2B/2B+/2Bi/2AB, use P3.1 (SCL) for serial clock and P3.0 (SDA) for serial data.

SCLINT interrupt is generated when SCL (P3.1) has a high-to-low transition and then keeps at low for

16 ´ 1/Fosc.

Fosc

8 MHz

10 MHz

SCL low

m

2 S

m

1.6 S

2. SIO2 port:

·

To support DDC2B/2B+/2Bi/2AB, use P4.4 (SCL) for serial clock and P4.5 (SDA) for serial data.

DDC1 Port

The DDC1 is a serial output port that supports DDC1 communication. To enable the DDC1 port,

ENDDC1 (bit 3 of CTRL1) should be set to '1'. Once previous eight data bits in the shift register and

IN

one null bit (the 9th bit) are shifted out to the SDA sequentially on each rising edge of the V signal,

the DDC1 control circuit loads the next data byte from the latch buffer (the DDC1 register) to the shift

register and generates a DDC1INT signal to the CPU. In the interrupt service routine, the S/W should

fetch the next byte of EDID data and write it to the DDC1 register. If ENDDC1 is cleared, the shift

register is stopped, and the SDA output is kept high. The bit DDC1B9 (bit 4 of CTRL2) decides the 9th

bit in a DDC transmission. If DDC1B9 is set, the 9th bit will be '1', otherwise '0'.

- 16 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]