WED3DL644V

White Electronic Designs

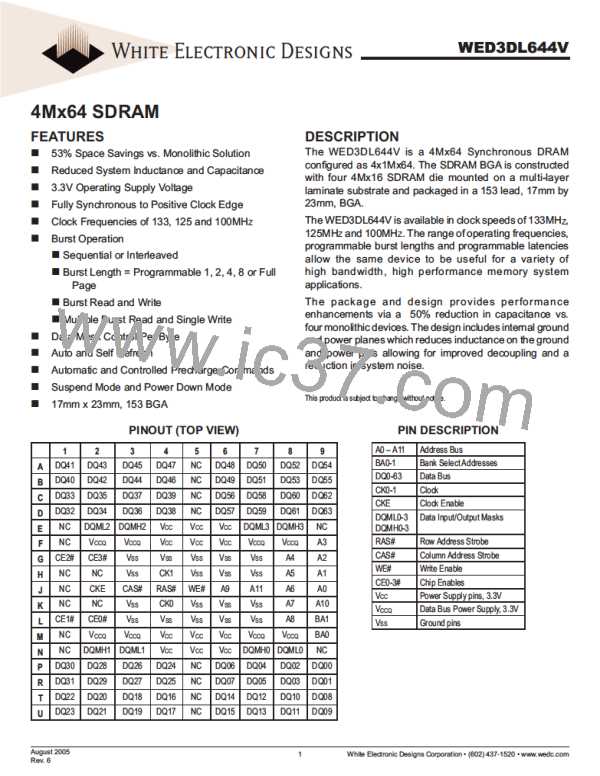

BURST DEFINITION

FIG.2

Mode Register Definition

Order of Accesses Within a Burst

Type = Sequential Type = Interleaved

Burst Starting Column

Length

Address

A11

11

A8

A7

A6 A5 A4

A3 A2

A1

A0

Address Bus

A10

A9

A0

0

0

2

0-1

1-0

0-1

1-0

9

8

6

5

4

1

10

7

3

2

0

Mode Register(Mx)

Reserved* WB OpMode

BT

Burst Length

CAS Latency

A1 A0

0

0

1

1

0

1

0

1

0-1-2-3

1-2-3-0

2-3-0-1

3-0-1-2

0-1-2-3

1-0-3-2

2-3-0-1

3-2-1-0

*Shouldprogram

M11, M10 = “ 0, 0”

to ensure compatibility

with future devices.

4

8

Burst Length

M2 M1 M0

M3 = 0

M3 = 1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

2

4

8

1

2

4

A2

0

0

0

0

1

1

1

1

A1 A0

8

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0-1-2-3-4-5-6-7

1-2-3-4-5-6-7-0

2-3-4-5-6-7-0-1

3-4-5-6-7-0-1-2

4-5-6-7-0-1-2-3

5-6-7-0-1-2-3-4

6-7-0-1-2-3-4-5

7-0-1-2-3-4-5-6

0-1-2-3-4-5-6-7

1-0-3-2-5-4-7-6

2-3-0-1-6-7-4-5

3-2-1-0-7-6-5-4

4-5-6-7-0-1-2-3

5-4-7-6-1-0-3-2

6-7-4-5-2-3-0-1

7-6-5-4-3-2-1-0

Reserved

Reserved

Reserved

Full Page

Reserved

Reserved

Reserved

Reserved

Burst Type

M3

0

Sequential

Interleaved

1

CASLatency

M6 M5 M4

Cn, Cn+1, Cn+2

Cn+3, Cn+4...

...Cn-1,

Reserved

Reserved

2

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Full

Page

(y)

n = A0 - A9/8/7

(location 0-y)

Not Supported

3

Cn...

Reserved

Reserved

Reserved

Reserved

M8

M7

0

M6-M0

Defined

-

Operating Mode

0

-

Standard Operation

-

All other states reserved

Write Burst Mode

M9

0

Programmed Burst Length

Single Location Access

1

August 2005

Rev. 6

5

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]

WEDC [ WHITE ELECTRONIC DESIGNS CORPORATION ]