TPS929160-Q1

ZHCSNG0 – APRIL 2023

www.ti.com.cn

VSUP

VBAT

INH

TX

EN

TX

RX

TCAN1043-Q1

TPS929160-Q1

RX

VIO

EN

VCC

VLDO

NSTB

NSTB

nSTB

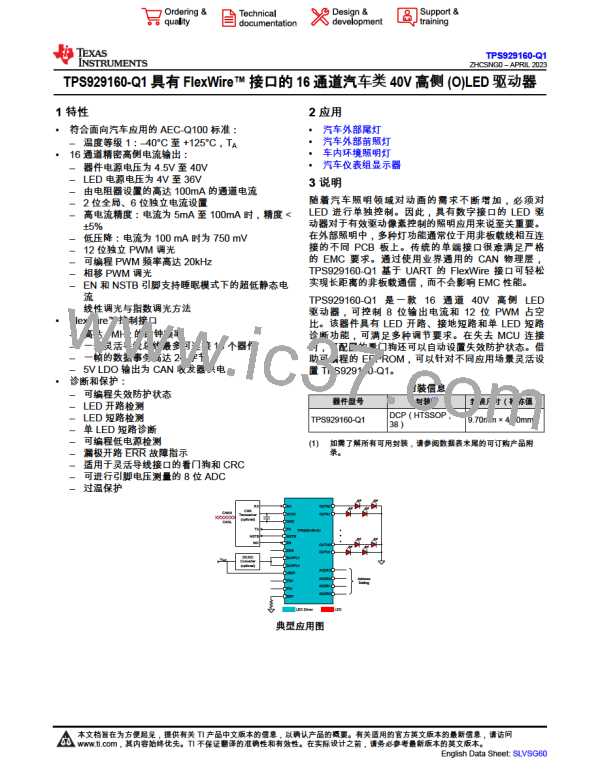

图 7-7. Sleep Mode Typical Application Diagram

Normal Mode

Sleep Mode

Normal Mode

VBAT

VSUP

TCAN1043-Q1

receive WUP

pull up INH

INH set to floating by TCAN1043-Q1

after Tgo-to-sleep time

EN

INH

Tgo-to-sleep

VLDO

VCC/VIO/EN

Write 1 to NSTB register

TPS929160-Q1 set NSTB

to floating

NSTB

nSTB

图 7-8. Sleep Mode Access and Exit Timing Diagram

7.3.7 Diagnostic and Protection in NORMAL state

The TPS929160-Q1 has full-diagnostics coverage for supply voltage, current output, and junction temperature.

In NORMAL state, the device detects all failures and reports the status out through the ERR or FLAG registers,

without any actions taken by the device except VBAT UVLO, supply undervoltage and overtemperature

protection. The master controller must handle all fault actions, for example, retry several times and shut down

the outputs if the error still exists. The fault behavior in NORMAL state can be found in 表 7-6.

7.3.7.1 VBAT Undervoltage Lockout Diagnostics in NORMAL state

When VBAT or VLDO voltage drops below its UVLO threshold, the device enters POR state. Upon voltage

recovery, the device automatically switches to INIT state with FLAG_POR and FLAG_ERR set to 1. The master

controller can write 1 to register CLRPOR to clear the FLAG_POR and FLAG_ERR, and the CLRPOR bit

automatically returns to 0.

7.3.7.2 Low-Supply Warning Diagnostics in NORMAL State

The TPS929160-Q1 continuously monitors the SUPPLY voltage and compares the results with internal threshold

V(LOWSUPTH) set by LOWSUPTH for low-supply voltage warning.

If the supply voltage is lower than threshold, the device pulls ERR pin down with one pulsed current sink for 50

µs to report the fault and set flag registers including FLAG_LOWSUP and FLAG_ERR to 1.

The fault is latched in flag registers. When the supply voltage rises above low-supply warning threshold, the

master controller must write 1 to register CLRFAULT to clear FLAG_LOWSUP and FLAG_ERR. The CLRFAULT

bit automatically returns to 0.

Copyright © 2023 Texas Instruments Incorporated

28

Submit Document Feedback

Product Folder Links: TPS929160-Q1

English Data Sheet: SLVSG60

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]