TMS3705

www.ti.com

11-07-22-003 – SCBS881B –JANUARY 2010–REVISED APRIL 2010

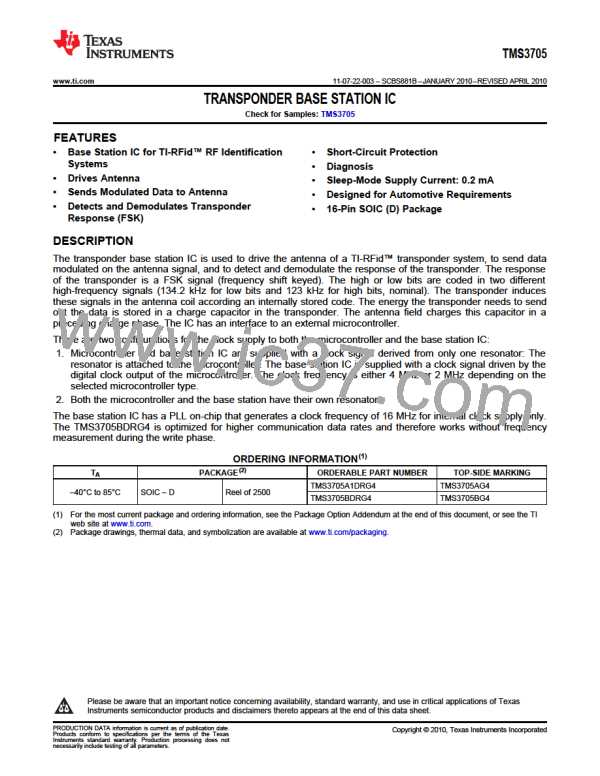

Diagnosis

The diagnosis is carried out during the charge phase to detect whether the full bridge and the antenna are

working. When the full bridge drives the antenna, the voltage across the coil exceeds the supply voltage so that

the voltage at the input of the RF amplifier is clamped by the ESD-protection diodes. For diagnosis, the SENSE

pin is loaded on-chip with a switchable resistor to ground so that the internal switchable resistor and the external

SENSE resistor form a voltage divider, while the internal resistor is switched off in read mode. When the voltage

drop across the internal resistor exceeds a certain value, the diagnosis block passes the frequency of its input

signal to the digital demodulator. The frequency of the diagnosis signal is accepted, if eight subsequent time can

be detected, all with their counter state within the range of 112 to 125, during the diagnosis time (at most 0.1

ms). The output signal is used during the charge phase only else it is ignored.

When the short-circuit protection switches off one of the full-bridge drivers, the diagnosis also indicates an

improper operation of the antenna by sending the same diagnostic byte to the microcontroller as for the other

failure mode.

During diagnosis, the antenna drivers are active. In synchronous mode the antenna drivers remain active up to 1

ms after the diagnosis is performed, without any respect to the logic state of the signal at TXCT (thus enabling

the microcontroller to clock out the diagnosis byte).

Power-On Reset

The power-on reset generates an internal reset signal to allow the control logic to start up in the defined way.

Frequency Divider

The frequency divider is a programmable divider that generates the carrier frequency for the full-bridge antenna

drivers. The default value for the division factor is the value 119 needed to provide the nominal carrier frequency

of 134.45 kHz generated from 16 MHz. The resolution for programming the division factor is one divider step that

corresponds to a frequency shift of about 1.1 kHz. The different division factors needed to cover the range of

frequencies for meeting the resonance frequency of the transponder are 114 to 124.

Digital Demodulator

The input signal of the digital demodulator comes from the limiter and is frequency-coded according to the high-

and low-bit sequence of the transmitted transponder code. The frequency of the input signal is measured by

counting the oscillation clock for the time period of the input signal. As the high-bit and low-bit frequencies are

specified with wide tolerances, the demodulator is designed to distinguish the high-bit and the low-bit frequency

by the shift between the two frequencies and not by the absolute values. The threshold between the high-bit and

the low-bit frequency is defined to be 6.5 kHz lower than the measured low-bit frequency and has a hysteresis of

±0.55 kHz.

The demodulator is controlled by the control logic. After the charge phase (that is during read or write phase) it

measures the time period of its input signal and waits for the transponder resonance-frequency measurement to

determine the counter state for the threshold between high-bit and low-bit frequency. Then the demodulator waits

for the occurrence of the start bit. For that purpose, the results of the comparisons between the measured time

periods and the threshold are shifted in a 12-bit shift register. The detection of the start bit comes into effect

when the contents of the shift register matches a specific pattern, indicating 8 subsequent periods below the

threshold immediately followed by 4 subsequent periods above the threshold. A 2-period digital filter is inserted in

front of the 12-bit shift register to make a start bit detection possible in case of a non-monotonous progression of

the time periods during a transition from low- to high-bit frequency.

The bit stream detected by the input stage of the digital demodulator passes a digital filter before being

evaluated. After demodulation, the serial bit flow received from the transponder is buffered byte-wise before

being sent to the microcontroller by SCI encoding.

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

5

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]