PCM1794A

ZHCSEE9B –AUGUST 2004–REVISED DECEMBER 2015

www.ti.com.cn

Application Information (continued)

Table 5. External Digital Filter Application Timing Requirements

MIN

20

7

MAX

UNIT

ns

t(BCY)

t(BCL)

t(BCH)

t(BL)

BCK pulse-cycle time

BCK pulse duration, LOW

BCK pulse duration, HIGH

BCK rising edge to WDCK falling edge

WDCK falling edge to BCK rising edge

DATA setup time

ns

7

ns

5

ns

t(LB)

5

ns

t(DS)

t(DH)

5

ns

DATA hold time

5

ns

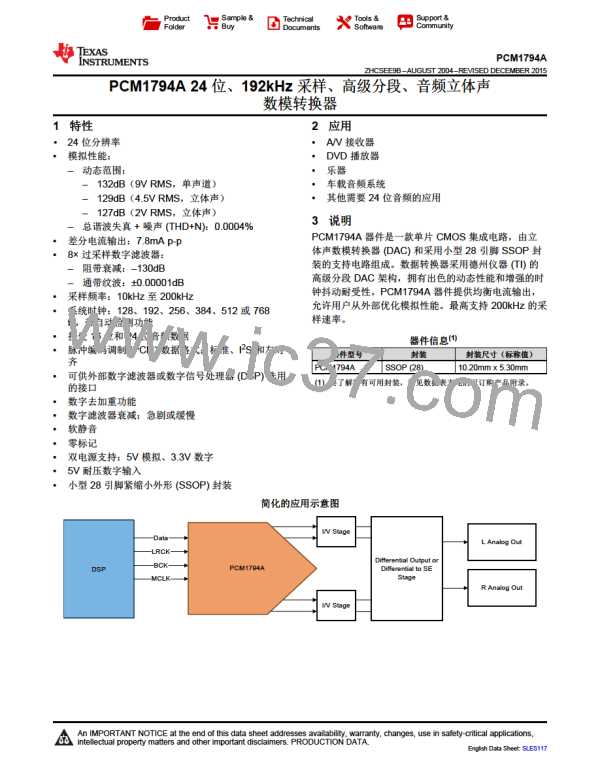

8.1.3.2 Audio Format

The PCM1794A device in the external digital filter interface mode supports right-justified audio formats, including

24-bit audio data, as shown in Figure 30.

1/4 f or 1/8 f

S

S

WDCK

BCK

Audio Data Word = 24-Bit

23 24

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

DATA

MSB

LSB

Figure 30. Audio Data Input Format for External Digital Filter (Internal DF Bypass Mode) Application

24

Copyright © 2004–2015, Texas Instruments Incorporated

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]