ADS1115-Q1

SBAS563 –DECEMBER 2011

www.ti.com

OVERVIEW

switched-capacitor ΔΣ modulator followed by a digital

filter. Input signals are compared to the internal

The ADS1115-Q1 is a small, low-power, 16-bit,

delta-sigma (ΔΣ) analog-to-digital converters (ADCs).

The ADS1115-Q1 is an easy to configure and design

into a wide variety of applications, and allow precise

measurements to be obtained with very little effort.

Both experienced and novice users of data

converters find designing with the ADS1115-Q1

intuitive and problem-free.

voltage reference. The digital filter receives

a

high-speed bitstream from the modulator and outputs

a code proportional to the input voltage.

The ADS1115-Q1 have two available conversion

modes: single-shot mode and continuous conversion

mode. In single-shot mode, the ADC performs one

conversion of the input signal upon request and

stores the value to an internal result register. The

device then enters a low-power shutdown mode. This

mode is intended to provide significant power savings

in systems that only require periodic conversions or

when there are long idle periods between

conversions. In continuous conversion mode, the

ADC automatically begins a conversion of the input

signal as soon as the previous conversion is

completed. The rate of continuous conversion is

equal to the programmed data rate. Data can be read

at any time and always reflect the most recent

completed conversion.

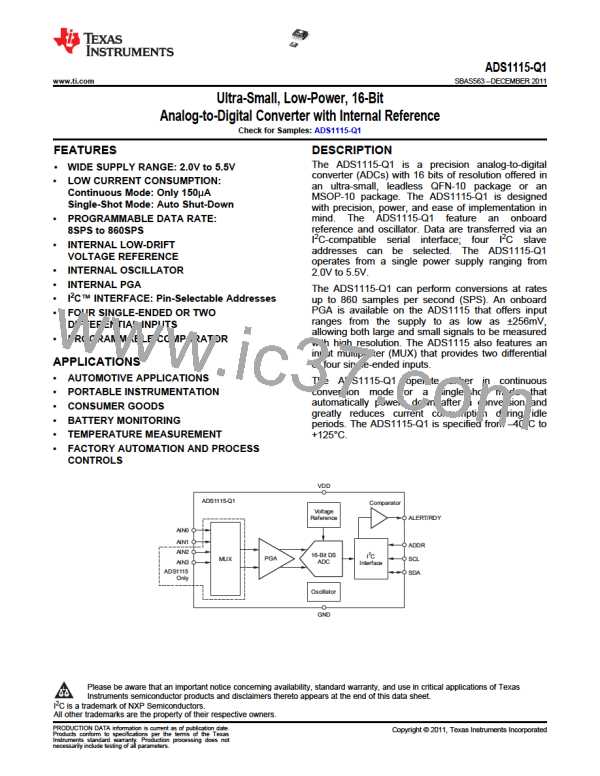

The ADS1115-Q1 consists of a ΔΣ analog-to-digital

(A/D) core with adjustable gain, an internal voltage

reference, a clock oscillator, and an I2C interface. An

additional feature available on the ADS1115-Q1 is a

programmable digital comparator that provides an

alert on a dedicated pin. All of these features are

intended to reduce required external circuitry and

improve performance. Figure 22 shows the

ADS1115-Q1 functional block diagram.

The ADS1115-Q1 A/D core measures a differential

signal, VIN, that is the difference of AINP and AINN. A

MUX is available on the ADS1115. This architecture

results in a strong attenuation in any common-mode

signals. The converter core consists of a differential,

VDD

ADS1115

Comparator

Voltage

Reference

ALERT/RDY

MUX

Gain = 2/3, 1,

2, 4, 8, or 16

AIN0

ADDR

SCL

I2C

Interface

16-Bit DS

PGA

AIN1

ADC

SDA

AIN2

AIN3

Oscillator

GND

Figure 22. ADS1115-Q1 Functional Block Diagram

10

Submit Documentation Feedback

Copyright © 2011, Texas Instruments Incorporated

Product Folder Link(s) :ADS1115-Q1

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]