STM32F302xx/STM32F303xx

Electrical characteristics

2

Table 62. I S characteristics (continued)

Symbol

Parameter

Conditions

Min

Max

Unit

(1)

tsu(SD_MR)

tsu(SD_SR)

Data input setup time

Data input setup time

Master receiver

Slave receiver

Master receiver

Slave receiver

9

2

0

0

(1)

(1)

th(SD_MR)

Data input hold time

(1)

th(SD_SR)

Slave transmitter

(after enable edge)

(1)

tv(SD_ST)

th(SD_ST)

tv(SD_MT)

th(SD_MT)

Data output valid time

Data output hold time

Data output valid time

Data output hold time

29

3

ns

Slave transmitter

(after enable edge)

(1)

(1)

(1)

12

2

Master transmitter

(after enable edge)

Master transmitter

(after enable edge)

1. Data based on characterization results, not tested in production.

2

(1)

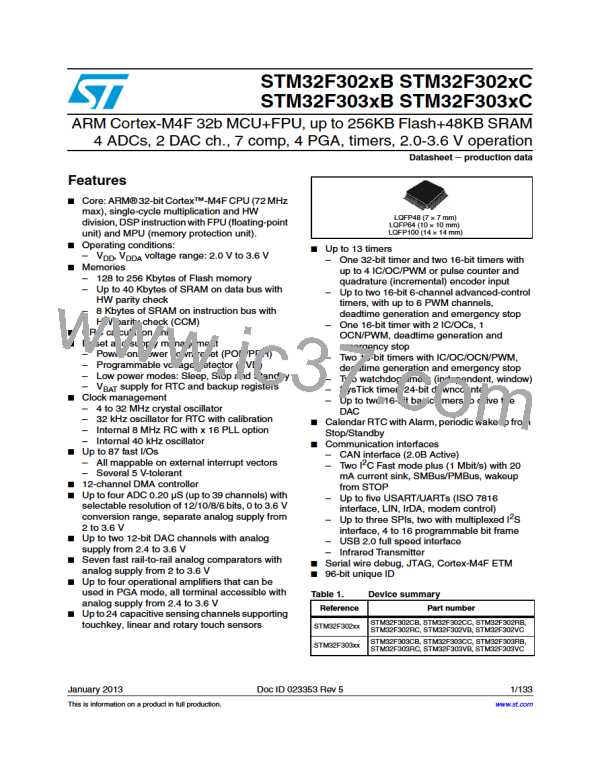

Figure 29. I S slave timing diagram (Philips protocol)

t

c(CK)

CPOL = 0

CPOL = 1

t

t

t

w(CKL)

h(WS)

w(CKH)

WS input

t

t

t

h(SD_ST)

t

v(SD_ST)

su(WS)

SD

transmit

(2)

LSB transmit

MSB transmit

MSB receive

Bitn transmit

LSB transmit

t

su(SD_SR)

h(SD_SR)

(2)

LSB receive

Bitn receive

LSB receive

SD

receive

ai14881b

1. Measurement points are done at 0.5VDD and with external CL=30 pF

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first

byte.

Doc ID 023353 Rev 5

101/133

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]