16 Mbit Concurrent SuperFlash + 2 / 4 Mbit SRAM ComboMemory

SST34HF1621 / SST34HF1641

Data Sheet

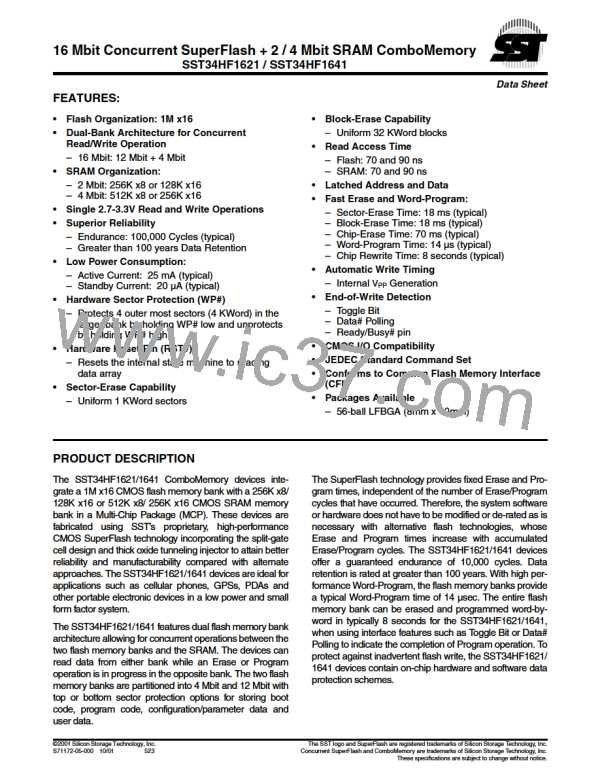

AC CHARACTERISTICS

TABLE 12: SRAM READ CYCLE TIMING PARAMETERS

SST34HF1621/1641-70

SST34HF1621/1641-90

Symbol

TRCS

Parameter

Min

Max

Min

Max

Units

ns

Read Cycle Time

70

90

TAAS

Address Access Time

70

70

35

70

90

90

45

90

ns

TBES

Bank Enable Access Time

Output Enable Access Time

UBS#, LBS# Access Time

BES# to Active Output

ns

TOES

ns

TBYES

ns

1

TBLZS

0

0

0

0

0

0

ns

1

TOLZS

Output Enable to Active Output

UBS#, LBS# to Active Output

BES# to High-Z Output

ns

1

TBYLZS

ns

1

TBHZS

25

25

35

35

35

45

ns

1

TOHZS

Output Disable to High-Z Output

UBS#, LBS# to High-Z Output

Output Hold from Address Change

ns

1

TBYHZS

ns

TOHS

10

10

ns

T12.3 523

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

TABLE 13: SRAM WRITE CYCLE TIMING PARAMETERS

SST34HF1621/1641-70

SST34HF1621/1641-90

Symbol

TWCS

TBWS

Parameter

Min

70

60

60

0

Max

Min

90

80

80

0

Max

Units

Write Cycle Time

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Bank Enable to End-of-Write

Address Valid to End-of-Write

Address Set-up Time

TAWS

TASTS

TWPS

Write Pulse Width

60

0

80

0

TWRS

TBYWS

TODWS

TOEWS

TDSS

Write Recovery Time

UBS#, LBS# to End-of-Write

Output Disable from WE# Low

Output Enable from WE# High

Data Set-up Time

60

80

30

40

0

30

0

0

40

0

TDHS

Data Hold from Write Time

ns

T13.3 523

©2001 Silicon Storage Technology, Inc.

S71172-05-000 10/01 523

14

SST [ SILICON STORAGE TECHNOLOGY, INC ]

SST [ SILICON STORAGE TECHNOLOGY, INC ]