16 Mbit Concurrent SuperFlash + 2/4/8 Mbit SRAM ComboMemory

SST34HF1602C / SST34HF1622C / SST34HF1642C

SST34HF1642D / SST34HF1682D / SST34HF1622S / SST34HF1642S

Advance Information

T

T

AA

RC

ADDRESS A

19-0

T

CE

BEF#

OE#

T

OE

T

OHZ

T

OLZ

V

IH

WE#

T

CHZ

T

OH

T

CLZ

HIGH-Z

HIGH-Z

DQ

15-0

DATA VALID

DATA VALID

1256 F07.0

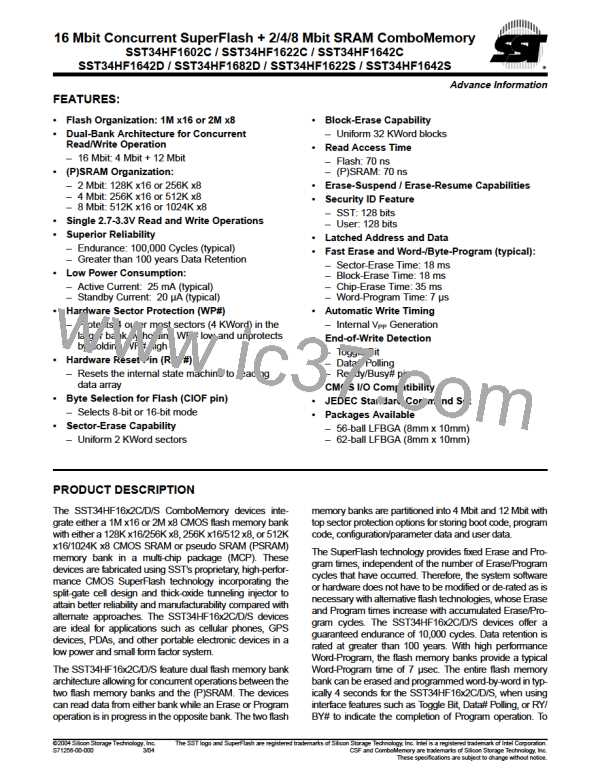

FIGURE 8: FLASH READ CYCLE TIMING DIAGRAM FOR WORD MODE

(FOR BYTE MODE A-1 = ADDRESS INPUT)

T

BP

5555

2AAA

5555

ADDR

ADDRESS A

19-0

T

AH

T

WP

WE#

T

WPH

T

AS

OE#

BEF#

T

CH

T

CS

T

BY

T

BR

RY/BY#

T

DS

T

DH

DQ

15-0

XXAA

XX55

XXA0

DATA

VALID

WORD

(ADDR/DATA)

1256 F08.0

Note: X can be V or V , but no other value.

IL

IH

FIGURE 9: FLASH WE# CONTROLLED WORD-PROGRAM CYCLE TIMING DIAGRAM FOR WORD MODE

(FOR BYTE MODE A-1 = ADDRESS INPUT)

©2004 Silicon Storage Technology, Inc.

S71256-00-000

3/04

22

SST [ SILICON STORAGE TECHNOLOGY, INC ]

SST [ SILICON STORAGE TECHNOLOGY, INC ]