2 Mbit Page-Mode EEPROM

SST29EE020 / SST29LE020 / SST29VE020

Data Sheet

T

T

RC

AA

ADDRESS A

17-0

T

CE

CE#

T

OE

OE#

T

T

OHZ

OLZ

V

IH

WE#

T

CHZ

T

OH

T

CLZ

HIGH-Z

HIGH-Z

DATA VALID

DATA VALID

DQ

7-0

307 ILL F03.0

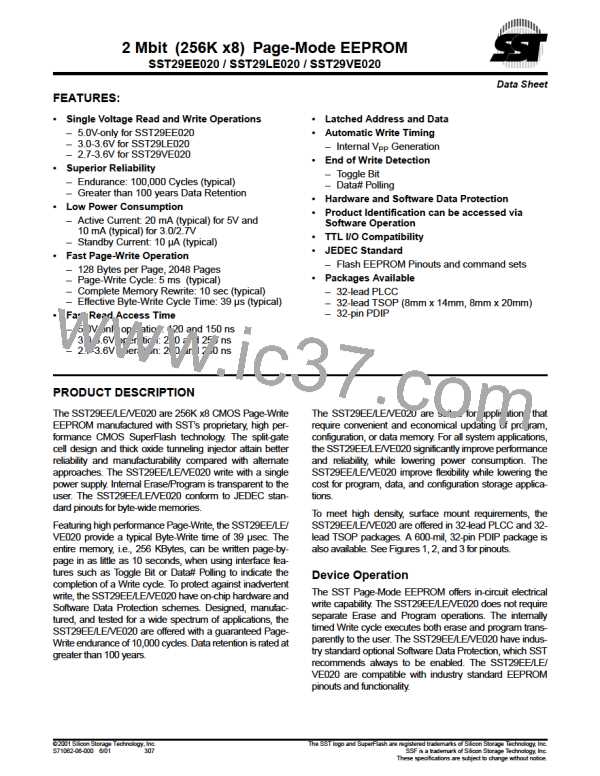

FIGURE 4: READ CYCLE TIMING DIAGRAM

Three-Byte Sequence for

Enabling SDP

T

AH

T

AS

ADDRESS A

5555 2AAA 5555

17-0

T

T

CS

CH

CE#

T

T

OEH

OES

OE#

WE#

T

WP

T

BLCO

T

BLC

T

DH

DQ

AA

55

A0

DATA VALID

7-0

T

WC

T

DS

SW0

SW1

SW2

BYTE 0

BYTE 1

BYTE 127

307 ILL F04.1

FIGURE 5: WE# CONTROLLED PAGE-WRITE CYCLE TIMING DIAGRAM

©2001 Silicon Storage Technology, Inc.

S71062-06-000 6/01 307

12

SST [ SILICON STORAGE TECHNOLOGY, INC ]

SST [ SILICON STORAGE TECHNOLOGY, INC ]