| 型号: | SST29VF010-120-4I-PH |

| PDF下载: | 下载PDF文件 查看货源 |

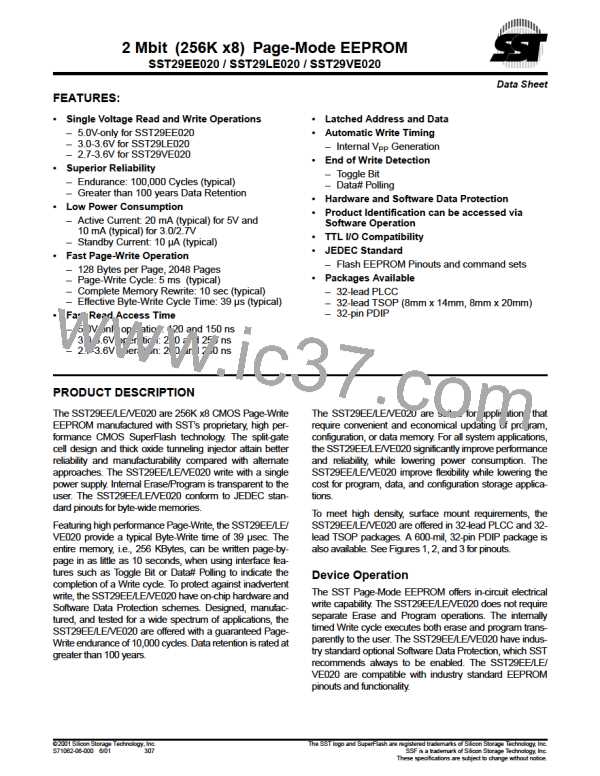

| 内容描述: | 2兆位( 256K ×8 )页面模式的EEPROM [2 Mbit (256K x8) Page-Mode EEPROM] |

| 分类和应用: | 可编程只读存储器电动程控只读存储器电可擦编程只读存储器 |

| 文件页数/大小: | 26 页 / 324 K |

| 品牌: |  SST [ SILICON STORAGE TECHNOLOGY, INC ] SST [ SILICON STORAGE TECHNOLOGY, INC ] |

专业IC领域供求交易平台:提供全面的IC Datasheet资料和资讯,Datasheet 1000万数据,IC品牌1000多家。