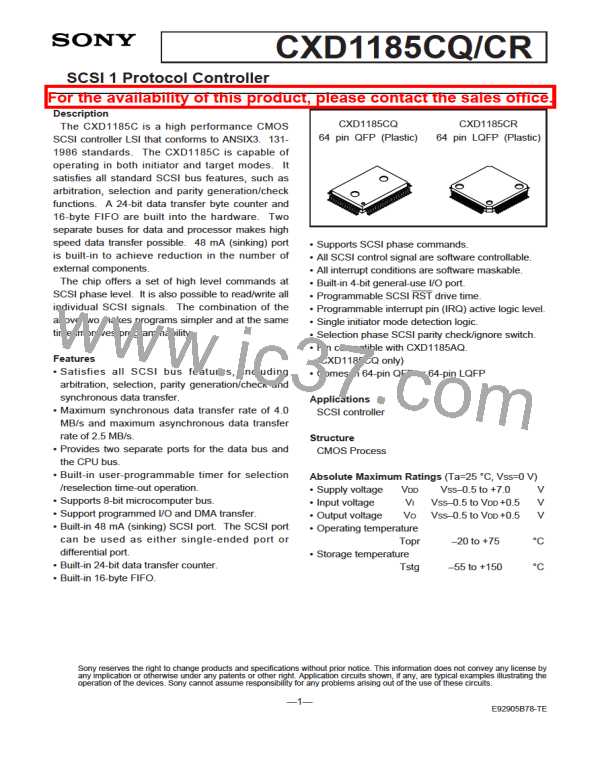

CXD1185CQ/CR

1-15. I/O port (RF : R/W)

This register is used for input/output switching of the general-use 4-bit port and for reading/writing the

contents of the port.

7

6

5

4

3

2

1

0

PCN3 PCN2 PCN1 PCN0 PRT3 PRT2 PRT1 PRT0

PCN3, PCN2, PCN1, PCN0 :

These bits are used for input/output switching of individual bits when Pins P3-P0 are used as a general-use

port. When a “1” is written to any of these bits, the corresponding port is set to the output mode.

All these bits are cleared when a hardware reset is performed. Note that first “0” must be written to all these

bits before writing a “1” to environment setting register bit 7 (DIFE).

PRT3, PRT2, PRT1, PRT0

This is the 4-bit I/O port.

:

The values written to whichever of these four bits have been set to output mode by PCN3-PCN0 are output

via Pins P3-P0. By reading these bits it is possible to monitor the values of Pins P3-P0 directly.

2. Command Description

This section gives description of all the commands supported by the CXD1185C.

With the exception of “Reset Chip”, the following commands can only be written to the command register

when the CIP bit in the status register (bit 0) is “0”.

2-1. Commands valid in any status

The following commands can be issued when the CXD1185C is in any of its three statuses : disconnected,

initiator or target.

• No Operation

This command has no effect on the CXD1185C.

However, the FNC bit is set when the command is completed.

• Reset Chip

This command initializes the CXD1185C.

Except for the environment setting register, all registers of the CXD1185C are cleared. If the clock division

ratio is changed in the environment setting register, this command must be executed.

This command can be executed regardless of the value of the CIP bit.

• Assert RST

This command drives the SCSI bus RST pin.

When this command is executed, interrupt request register 2 bit 5 (SRST) is set and an interrupt is

generated. The SCSI RST signal is active for 25 µs. However, if the RST signal drive duration needs to

be changed, it is necessary to set mode register bit 4 (TMSL) to “1” and write the drive duration to the

selection/reset timer register before executing this command.

• Flush FIFO

Initializes FIFO.

—19—

SONY [ SONY CORPORATION ]

SONY [ SONY CORPORATION ]