LC89057W-VF4A-E

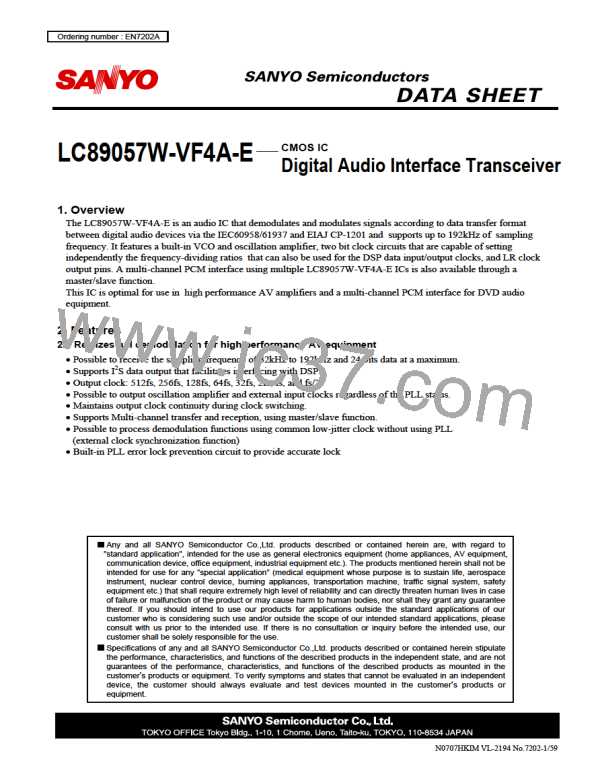

CCB address: 0xE8; Command address: 5; Demodulation function: Clock source; RDATA output setting

DI7

DI6

DI5

DI4

DI3

DI2

DI1

DI0

0

1

0

1

0

0

CAU

CAL

DI15

0

DI14

DI13

DI12

DI11

0

DI10

DI9

DI8

RDTMUT

RDTSTA

RDTSEL

RCKSEL

OCKSEL

SELMTD

SELMTD

OCKSEL

RCKSEL

RDTSEL

RDTSTA

RDTMUT

Setting of output clock source switching method

0: Switch R system and S system simultaneously according to OCKSEL (initial value)

1: Switch R system according to RCKSEL and fix S system to XIN source

Clock source setting when SELMTD = 0

0: Use XIN clock as source while PLL is unlocked (initial value)

1: Use XIN clock as source regardless of PLL status

Clock source setting when SELMTD = 1

0: Use XIN clock as source while PLL is unlocked (initial value)

1: Use XIN clock as source regardless of PLL status

RDATA output setting while PLL is unlocked

0: Output SDIN data while PLL is unlocked (initial value)

1. Mute while PLL is unlocked

RDATA output setting

0: According to RDTSEL (initial value)

1: Output SDIN input data regardless of PLL status

RDATA mute setting

0: Output data selected with RDTSEL

1: Muted

•

When the oscillation amplifier is set to the permanent continuous operation mode with AMPOPR[1:0] or fs changes

are set not to be reflected to the error flag with FSERR, OCKSEL and RCKSEL can switch the clock source while

maintaining the RERR status. However, if none of these settings is made, RERR outputs an error once when switching

occurs.

•

•

To input data to SDIN, select a clock synchronized with the SDIN input data.

The XIN source can be switched while maintaining the PLL locked status. However, since switching between clock

and data output can be set independently, it is recommended to select mute or SDIN data for the output data when

XIN source is switched.

•

If the oscillation amplifier is set to stop automatically when the PLL gets locked, XIN source switching from the PLL

locked status is executed after the oscillation is stabilized. Moreover, switching of output data at this time is subject to

XIN source switching.

No.7202-43/59

SANYO [ SANYO SEMICON DEVICE ]

SANYO [ SANYO SEMICON DEVICE ]