K9F5608U0B-VCB0,VIB0,FCB0,FIB0

K9F5608Q0B-DCB0,DIB0,HCB0,HIB0

K9F5608U0B-YCB0,YIB0,PCB0,PIB0

K9F5608U0B-DCB0,DIB0,HCB0,HIB0

K9F5616Q0B-DCB0,DIB0,HCB0,HIB0

K9F5616U0B-YCB0,YIB0,PCB0,PIB0

K9F5616U0B-DCB0,DIB0,HCB0,HIB0

FLASH MEMORY

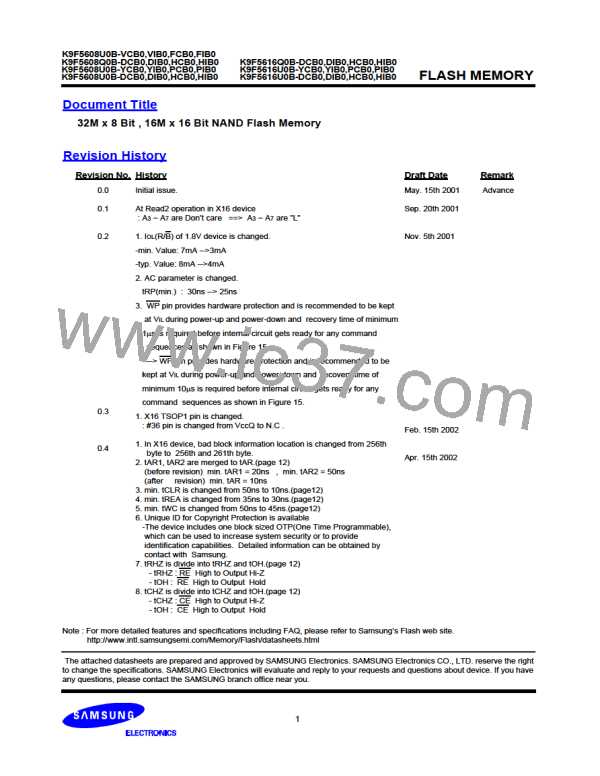

Figure 1-2. K9F5616X0B (X16) FUNCTIONAL BLOCK DIAGRAM

VCC

VSS

X-Buffers

A9 - A24

Latches

256M + 8M Bit

NAND Flash

ARRAY

& Decoders

Y-Buffers

Latches

A0 - A7

& Decoders

(256 + 8)Word x 65536

Page Register & S/A

Y-Gating

Command

Command

Register

VCC/VCCQ

VSS

I/O Buffers & Latches

Global Buffers

CE

RE

WE

Control Logic

& High Voltage

Generator

I/0 0

Output

Driver

I/0 15

CLE ALE

WP

Figure 2-2. K9F5616X0B (X16) ARRAY ORGANIZATION

1 Block =32 Pages

= (8K + 256) Word

1 Page = 264 Word

1 Block = 264 Word x 32 Pages

= (8K + 256) Word

1 Device = 264Words x 32Pages x 2048 Blocks

= 264 Mbits

64K Pages

(=2,048 Blocks)

Page Register

(=256 Words)

16 bit

256Word

8 Word

8 Word

I/O 0 ~ I/O 15

Page Register

256 Word

I/O 0

A0

I/O 1

A1

I/O 2

A2

I/O 3

I/O 4

A4

I/O 5

A5

I/O 6

A6

I/O 7

A7

I/O8 to 15

1st Cycle

2nd Cycle

3rd Cycle

A3

L*

L*

L*

Column Address

Row Address

(Page Address)

A9

A10

A18

A11

A19

A12

A20

A13

A21

A14

A22

A15

A23

A16

A24

A17

NOTE : Column Address : Starting Address of the Register.

* L must be set to "Low".

9

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]