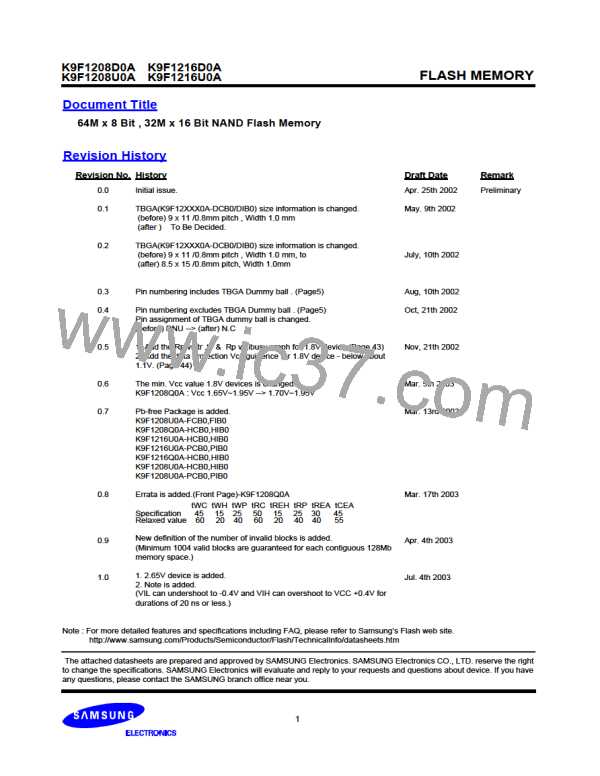

K9F1208D0A K9F1216D0A

K9F1208U0A K9F1216U0A

FLASH MEMORY

VALID BLOCK

Parameter

Symbol

Min

Typ.

Max

Unit

Valid Block Number

NVB

4,026

-

4,096

Blocks

NOTE :

1. The device may include invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is pre-

sented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase or program

factory-marked bad blocks. Refer to the attached technical notes for a appropriate management of invalid blocks.

2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block, does not require Error Correction up to 1K Program/Erase

cycles.

3. Minimum 1004 valid blocks are guaranteed for each contiguous 128Mb memory space.

AC TEST CONDITION

(K9F12XXX0A-XCB0 :TA=0 to 70°C, K9F12XXX0A-XIB0:TA=-40 to 85°C

K9F12XXD0A : Vcc=2.4V~2.9V , K9F12XXU0A : Vcc=2.7V~3.6V unless otherwise noted)

Parameter

K9F12XXD0A

0V to VccQ

5ns

K9F12XXU0A

0.4V to 2.4V

5ns

Input Pulse Levels

Input Rise and Fall Times

Input and Output Timing Levels

VccQ/2

1.5V

K9F12XXD0A:Output Load (VccQ:2.65V +/-10%)

K9F12XXU0A:Output Load (VccQ:3.0V +/-10%)

1 TTL GATE and CL=30pF1 TTL GATE and CL=50pF

1 TTL GATE and CL=100pF

K9F12XXU0A:Output Load (VccQ:3.3V +/-10%)

-

CAPACITANCE(TA=25°C, VCC=2.65V/3.3V, f=1.0MHz)

Item

Symbol

Test Condition

Min

Max

10

Unit

pF

Input/Output Capacitance

Input Capacitance

CI/O

VIL=0V

-

-

CIN

VIN=0V

10

pF

NOTE : Capacitance is periodically sampled and not 100% tested.

MODE SELECTION

CLE

H

L

ALE

L

CE

L

WE

RE

H

WP

X

Mode

Command Input

Read Mode

Write Mode

H

L

L

H

X

Address Input(4clock)

Command Input

H

L

L

H

H

H

L

L

H

H

Address Input(4clock)

L

L

H

H

Data Input

Data Output

L

L

L

H

H

X

L

L

L

H

H

X

During Read(Busy) on K9F1208U0A-Y,P,V,F or K9F1208D0A-Y,P

During Read(Busy) on the devices except K9F1208U0A-Y,P,V,F or

K9F1208D0A-Y,P

X

X

X

X

X

X

X

X

X

X

X

X

X

X

H

X

X

X

X

X

X

X

X

H

During Program(Busy)

During Erase(Busy)

Write Protect

H

L

X(1)

X

(2)

Stand-by

0V/VCC

NOTE : 1. X can be VIL or VIH.

2. WP should be biased to CMOS high or CMOS low for standby.

13

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]