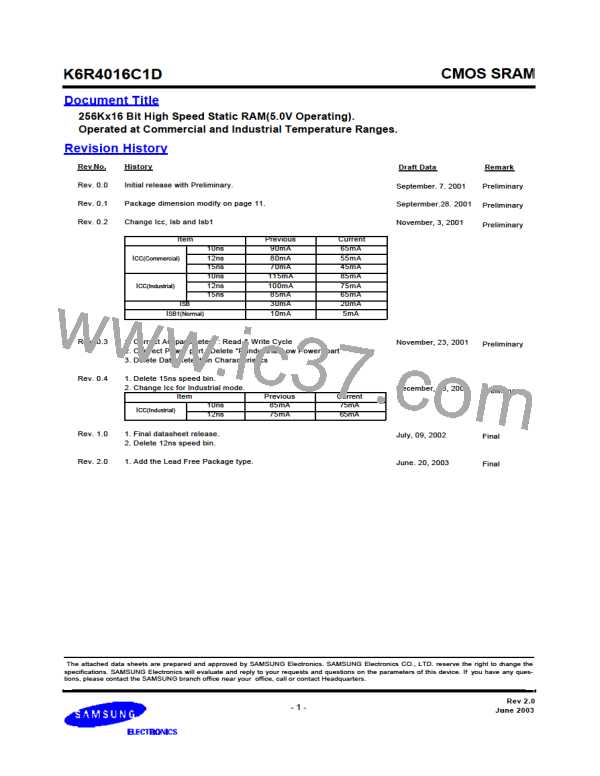

PRELIMPreliminaryPPPPPPPPPINARY

CMOS SRAM

K6R4016C1D

WRITE CYCLE*

K6R4016C1D-10

Parameter

Symbol

Unit

Min

10

7

Max

Write Cycle Time

tWC

tCW

tAS

-

-

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Chip Select to End of Write

Address Set-up Time

0

-

Address Valid to End of Write

Write Pulse Width(OE High)

Write Pulse Width(OE Low)

Write Recovery Time

tAW

tWP

tWP1

tWR

tWHZ

tDW

tDH

7

-

7

-

10

0

-

-

Write to Output High-Z

0

5

-

Data to Write Time Overlap

Data Hold from Write Time

End of Write to Output Low-Z

5

0

-

tOW

3

-

* The above parameters are also guaranteed at industrial temperature range.

TIMING DIAGRAMS

TIMING WAVEFORM OF READ CYCLE(1) (Address Controlled, CS=OE=VIL, WE=VIH, UB, LB=VIL)

tRC

Address

tAA

tOH

Data Out

Previous Valid Data

Valid Data

TIMING WAVEFORM OF READ CYCLE(2) (WE=VIH)

tRC

Address

tAA

tCO

tHZ(3,4,5)

CS

tBHZ(3,4,5)

tBA

UB, LB

OE

tBLZ(4,5)

tOHZ

tOE

tOLZ

tOH

tLZ(4,5)

Data out

High-Z

Valid Data

Rev 2.0

June 2003

- 7 -

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]